Pin description, Pwm base addresses, Register description – NXP Semiconductors LPC24XX UM10237 User Manual

Page 637: Table 25–554, Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

637 of 792

NXP Semiconductors

UM10237

Chapter 25: LPC24XX Pulse Width Modulator PWM0/PWM1

[1]

Identical to single edge mode in this case since Match 0 is the neighboring match register. Essentially,

PWM1 cannot be a double edged output.

[2]

It is generally not advantageous to use PWM channels 3 and 5 for double edge PWM outputs because it

would reduce the number of double edge PWM outputs that are possible. Using PWM 2, PWM4, and

PWM6 for double edge PWM outputs provides the most pairings.

4.

Pin description

gives a brief summary of each of PWM related pins.

5.

PWM base addresses

6.

Register description

The PWM0 and PWM1 function adds new registers and registers bits as shown in

below.

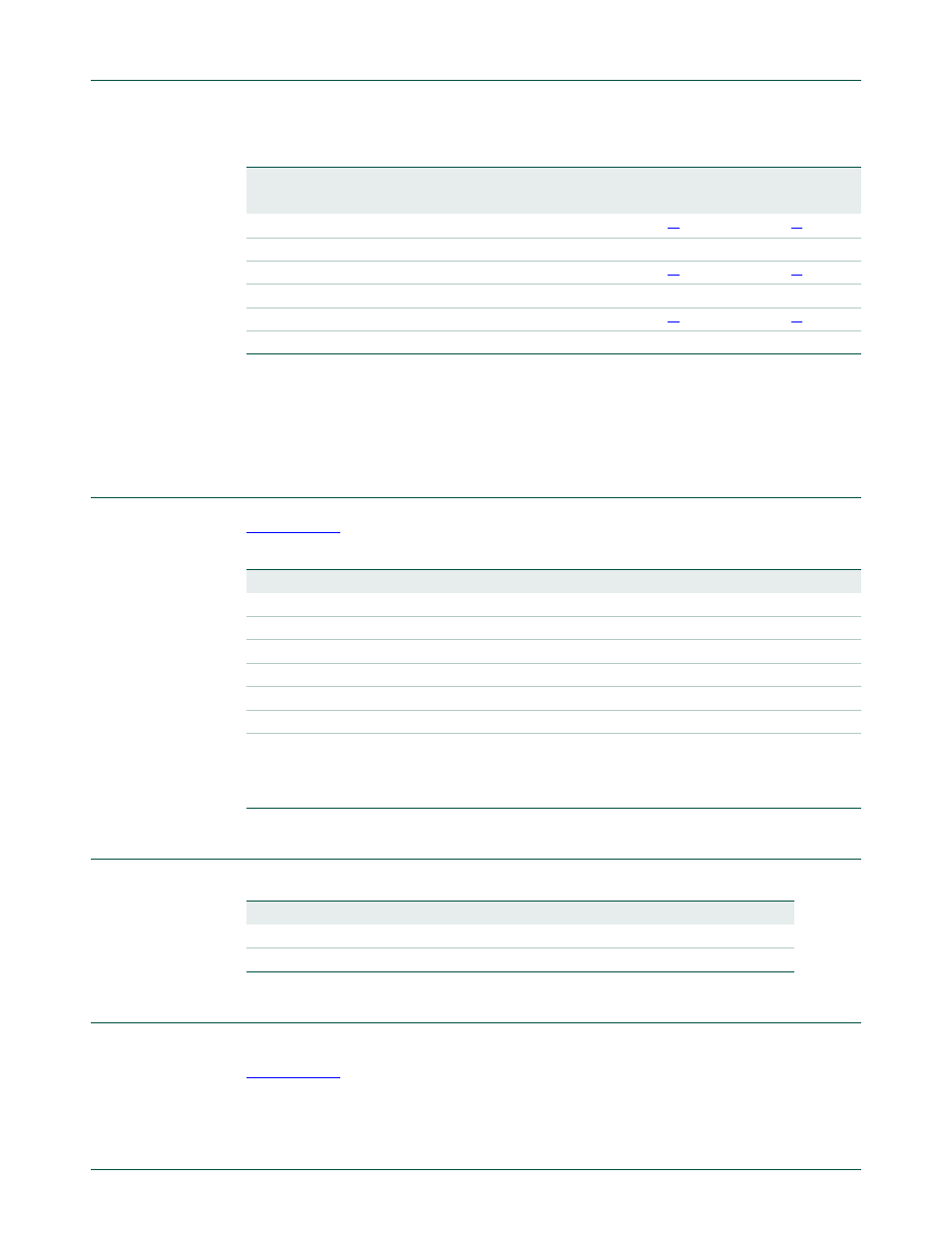

Table 554. Set and reset inputs for PWM flip-flops

PWM Channel

Single Edge PWM (PWMSELn = 0)

Double Edge PWM (PWMSELn = 1)

Set by

Reset by

Set by

Reset by

1

Match 0

Match 1

Match 0

Match 1

2

Match 0

Match 2

Match 1

Match 2

3

Match 0

Match 3

Match 2

Match 3

4

Match 0

Match 4

Match 3

Match 4

5

Match 0

Match 5

Match 4

Match 5

6

Match 0

Match 6

Match 5

Match 6

Table 555. Pin summary

Pin

Type

Description

PWM0/1[1]

Output

Output from PWM channel 1.

PWM0/1[2]

Output

Output from PWM channel 2.

PWM0/1[3]

Output

Output from PWM channel 3.

PWM0/1[4]

Output

Output from PWM channel 4.

PWM0/1[5]

Output

Output from PWM channel 5.

PWM0/1[6]

Output

Output from PWM channel 6.

PCAP0[0]

PCAP1[1:0]

Input

Capture Inputs. A transition on a capture pin can be configured to load

the corresponding Capture register with the value of the Timer Counter

and optionally generate an interrupt. PWM0 brings out one capture

input, PWM1 brings out 2 capture inputs.

Table 556: Addresses for PWM 0 and 1

PWM

Base addresses

0

0xE001 4000

1

0xE001 8000