3 receive filter register definitions, Table 11–221, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 236

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

236 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

7.2.17 Flow Control Status Register (FlowControlStatus - 0xFFE0 0174)

The Flow Control Status register (FlowControlStatus) is a Read Only register with an

address of 0xFFE0 8174.

lists the bit definitions of the register.

7.3 Receive filter register definitions

7.3.1 Receive Filter Control Register (RxFilterCtrl - 0xFFE0 0200)

The Receive Filter Control register (RxFilterCtrl) has an address of 0xFFE0 0200.

lists the definition of the individual bits in the register.

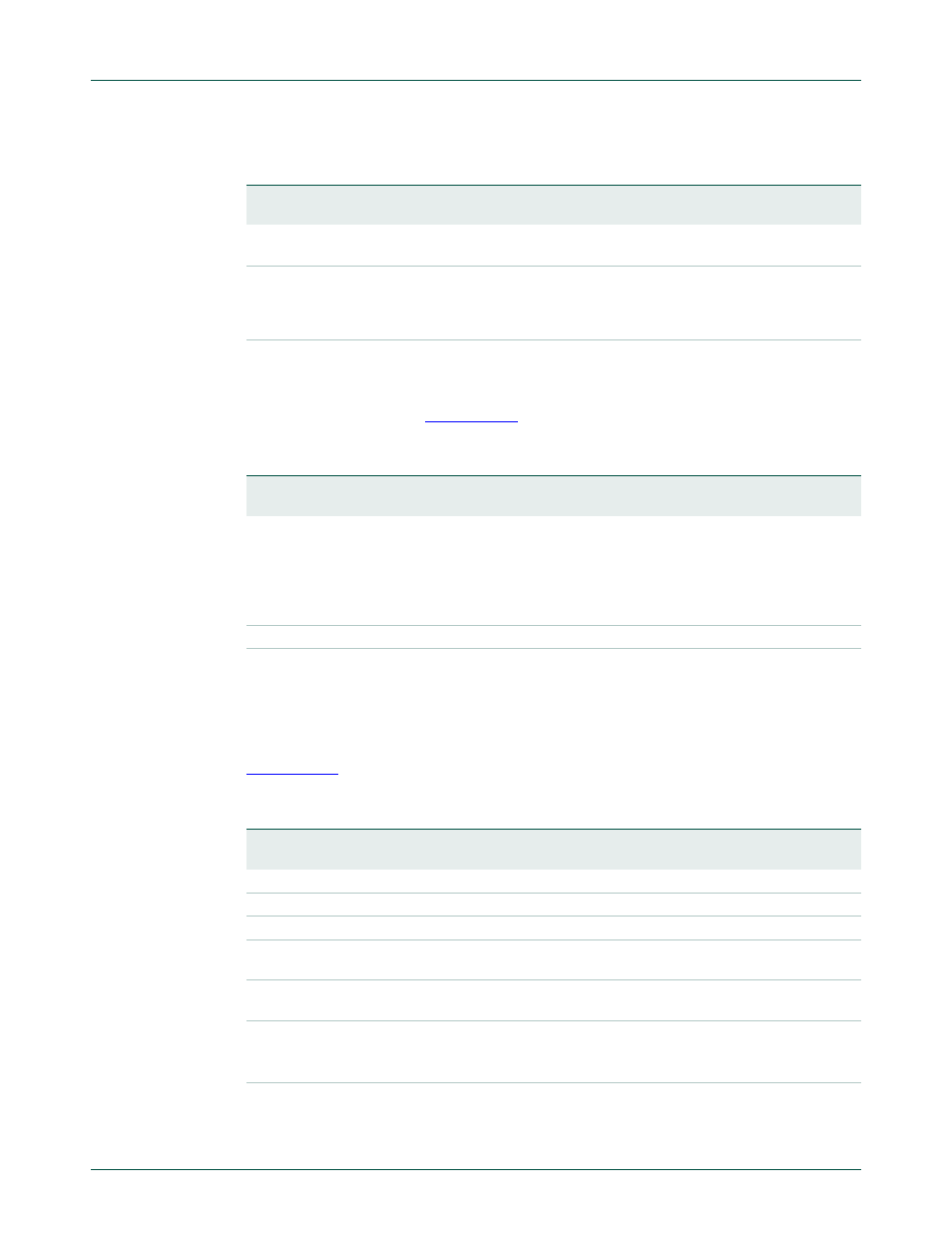

Table 221. Flow Control Counter register (FlowControlCounter - address 0xFFE0 0170) bit

description

Bit

Symbol

Function

Reset

value

15:0

MirrorCounter

In full duplex mode the MirrorCounter specifies the number

of cycles before re-issuing the Pause control frame.

0x0

31:16

PauseTimer In

full-duplex

mode

the PauseTimer specifies the value

that is inserted into the pause timer field of a pause flow

control frame. In half duplex mode the PauseTimer

specifies the number of backpressure cycles.

0x0

Table 222. Flow Control Status register (FlowControlStatus - address 0xFFE0 8174) bit

description

Bit

Symbol

Function

Reset

value

15:0

MirrorCounterCurrent In full duplex mode this register represents the current

value of the datapath’s mirror counter which counts up to

the value specified by the MirrorCounter field in the

FlowControlCounter register. In half duplex mode the

register counts until it reaches the value of the PauseTimer

bits in the FlowControlCounter register.

0x0

31:16

-

Unused

0x0

Table 223. Receive Filter Control register (RxFilterCtrl - address 0xFFE0 0200) bit

description

Bit

Symbol

Function

Reset

value

0

AcceptUnicastEn

When set to ’1’, all unicast frames are accepted.

0

1

AcceptBroadcastEn

When set to ’1’, all broadcast frames are accepted.

0

2

AcceptMulticastEn

When set to ’1’, all multicast frames are accepted.

0

3

AcceptUnicastHashEn

When set to ’1’, unicast frames that pass the imperfect

hash filter are accepted.

0

4

AcceptMulticastHashEn

When set to ’1’, multicast frames that pass the

imperfect hash filter are accepted.

0

5

AcceptPerfectEn

When set to ’1’, the frames with a destination address

identical to the

station address are accepted.

0

11:6

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA