Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 37

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

37 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

Masters with the same priority value are scheduled on a round-robin basis.

[1]

Allowed values for nn are: 10 (high priority) and 01 (low priority).

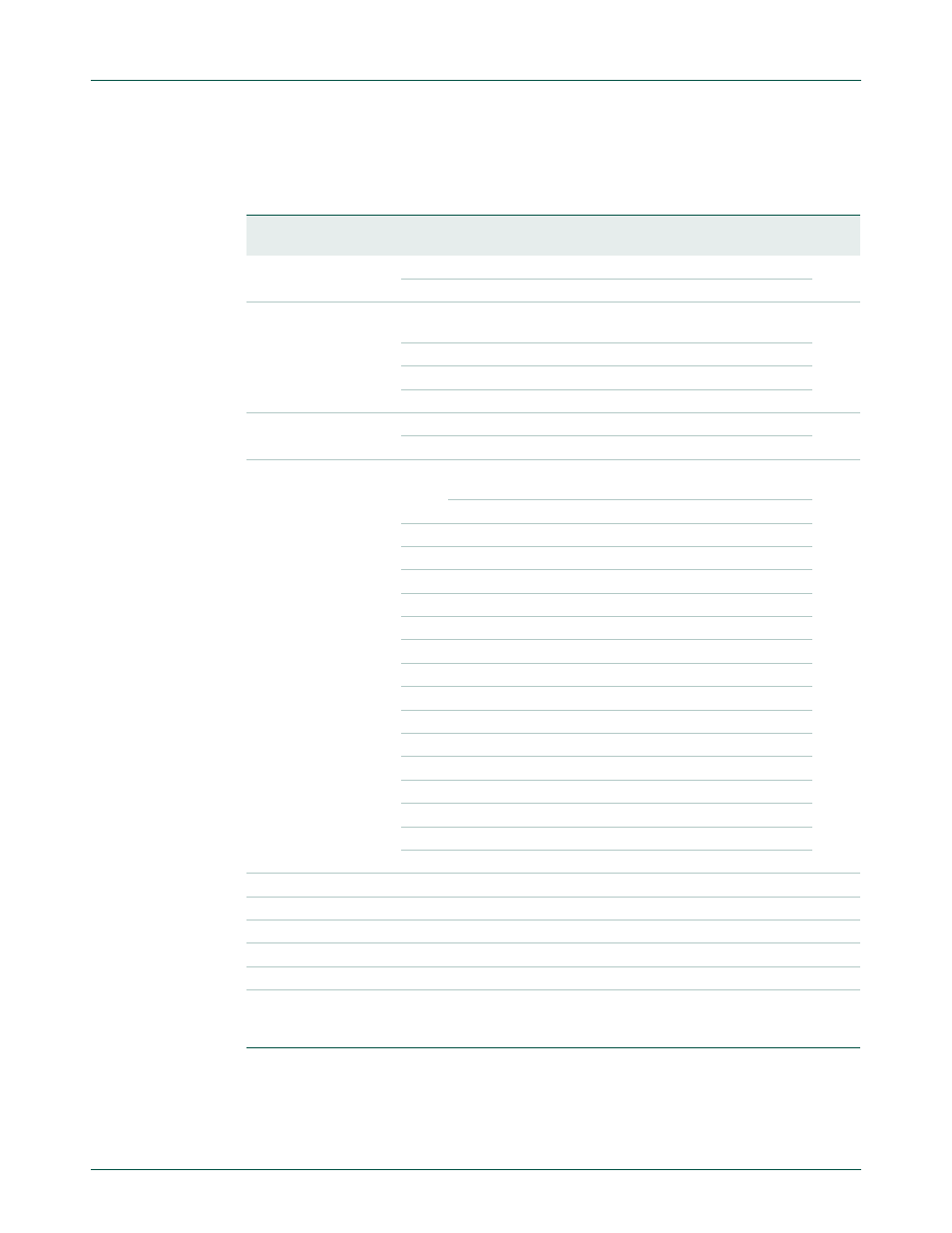

Table 35.

AHB Arbiter Configuration register 2 (AHBCFG2 - address 0xE01F C18C) bit

description

Bit

Symbol

Value Description

Reset

value

0

scheduler

0

Priority scheduling.

1

1

Uniform (round-robin) scheduling.

2:1

break_burst

00

Break all defined length bursts (the CPU does not create

defined bursts).

10

01

Break all defined length bursts greater than four-beat.

10

Break all defined length bursts greater than eight-beat.

11

Never break defined length bursts.

3

quantum_type

0

A quantum is an AHB clock.

0

1

A quantum is an AHB bus cycle.

7:4

quantum_size

Controls the type of arbitration and the number of quanta

before re-arbiration occurs.

0100

0000

Preemptive, re-arbitrate after 1 AHB quantum.

0001

Preemptive, re-arbitrate after 2 AHB quanta.

0010

Preemptive, re-arbitrate after 4 AHB quanta.

0011

Preemptive, re-arbitrate after 8 AHB quanta.

0100

Preemptive, re-arbitrate after 16 AHB quanta.

0101

Preemptive, re-arbitrate after 32 AHB quanta.

0110

Preemptive, re-arbitrate after 64 AHB quanta.

0111

Preemptive, re-arbitrate after 128 AHB quanta.

1000

Preemptive, re-arbitrate after 256 AHB quanta.

1001

Preemptive, re-arbitrate after 512 AHB quanta.

1010

Preemptive, re-arbitrate after 1024 AHB quanta.

1011

Preemptive, re-arbitrate after 2048 AHB quanta.

1100

Preemptive, re-arbitrate after 4096 AHB quanta.

1101

Preemptive, re-arbitrate after 8192 AHB quanta.

1110

Preemptive, re-arbitrate after 16384 AHB quanta.

1111

Non- preemptive, infinite AHB quanta.

9:8

default_master

nn

Master 2 (Ethernet) is the default master.

01

11:10 -

-

Reserved.

-

13:12 EP1

nn

External priority for master 1 (CPU).

00

15:14 -

-

Reserved.

-

17:16 EP2

nn

External priority for master 2 (Ethernet).

00

31:18 -

-

Reserved. User software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA