Table 26–569, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 651

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

651 of 792

NXP Semiconductors

UM10237

Chapter 26: LPC24XX Real-Time Clock (RTC) and battery RAM

6.2.2 Clock Tick Counter Register (CTCR - 0xE002 4004)

The Clock Tick Counter is read only. It can be reset to zero through the Clock Control

Register (CCR). The CTC consists of the bits of the clock divider counter.

If the RTC is driven by the external 32.786 kHz oscillator, subsequent read operations of

the CTCR may yield an incorrect result. The CTCR is implemented as a 15-bit ripple

counter so that not all 15 bits change simultaneously. The LSB changes first, then the

next, and so forth. Since the 32.786 kHz oscillator is asynchronous to the CPU clock, it is

possible for a CTC read to occur during the time when the CTCR bits are changing

resulting in an incorrect large difference between back-to-back reads.

If the RTC is driven by the PCLK, the CPU and the RTC are synchronous because both of

their clocks are driven from the PLL output. Therefore, incorrect consecutive reads can

not occur.

6.2.3 Clock Control Register (CCR - 0xE002 4008)

The clock register controls the operation of the clock divide circuit. Each bit of the clock

register is described in

6.2.4 Counter Increment Interrupt Register (CIIR - 0xE002 400C)

The Counter Increment Interrupt Register (CIIR) gives the ability to generate an interrupt

every time a counter is incremented. This interrupt remains valid until cleared by writing a

one to bit zero of the Interrupt Location Register (ILR[0]).

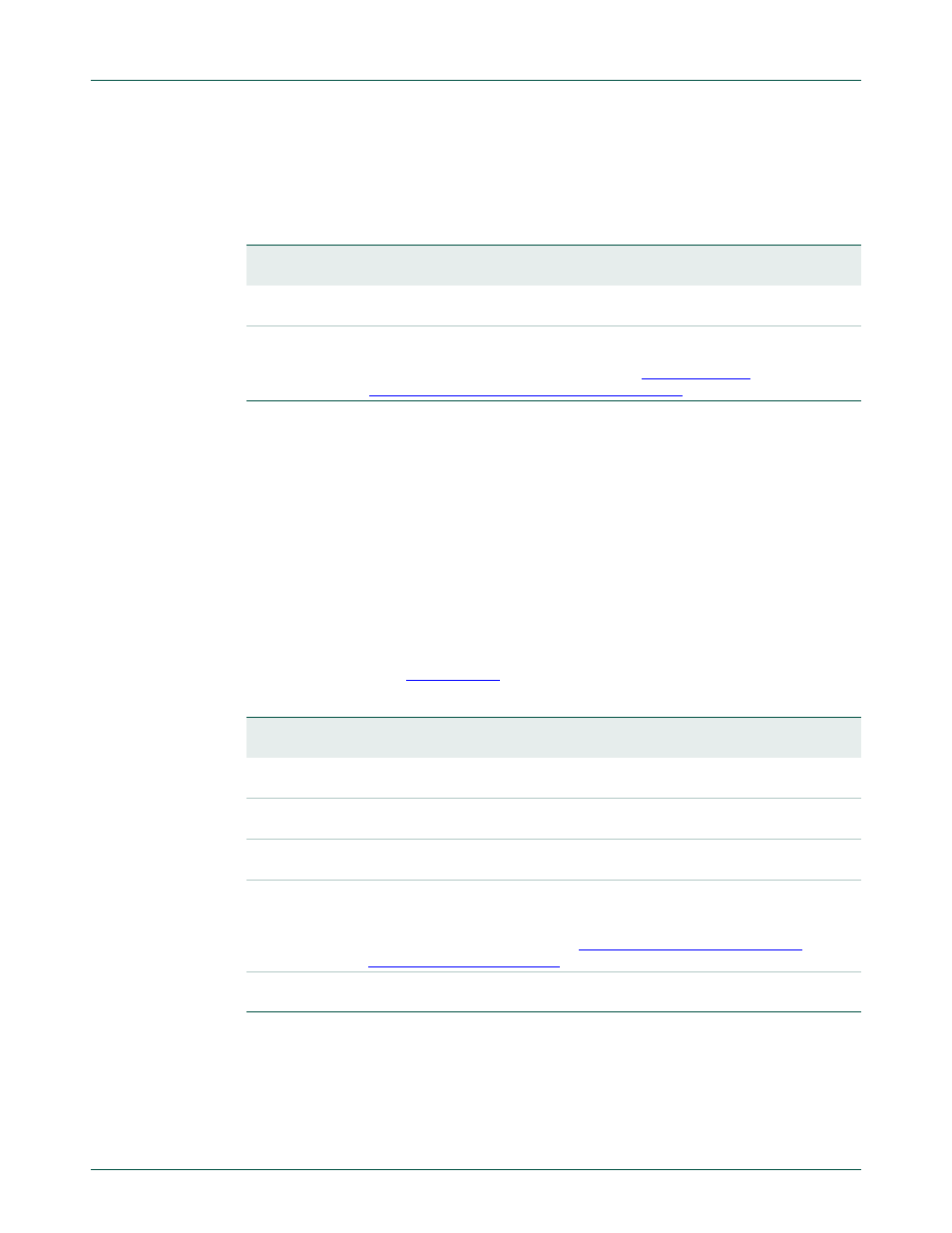

Table 568. Clock Tick Counter Register (CTCR - address 0xE002 4004) bit description

Bit

Symbol

Description

Reset

value

0

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

15:1

Clock Tick

Counter

Prior to the Seconds counter, the CTC counts 32,768 clocks per

second. Due to the RTC Prescaler, these 32,768 time increments may

not all be of the same duration. Refer to the

“Reference Clock Divider (Prescaler)” on page 656

for details.

NA

Table 569. Clock Control Register (CCR - address 0xE002 4008) bit description

Bit

Symbol

Description

Reset

value

0

CLKEN

Clock Enable. When this bit is a one the time counters are enabled.

When it is a zero, they are disabled so that they may be initialized.

NA

1

CTCRST

CTC Reset. When one, the elements in the Clock Tick Counter are

reset. The elements remain reset until CCR[1] is changed to zero.

NA

3:2

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

4

CLKSRC

If this bit is 0, the Clock Tick Counter takes its clock from the Prescaler,

as on earlier devices in the NXP Embedded ARM family. If this bit is 1,

the CTC takes its clock from the 32 kHz oscillator that’s connected to

the RTCX1 and RTCX2 pins (see

Section 26–9 “RTC external 32 kHz

oscillator component selection”

for hardware details).

NA

7:5

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA