Contact information – NXP Semiconductors LPC24XX UM10237 User Manual

Page 2

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

2 of 792

Contact information

For more information, please visit:

http://www.nxp.com

For sales office addresses, please send an email to:

NXP Semiconductors

UM10237

LPC24XX User manual

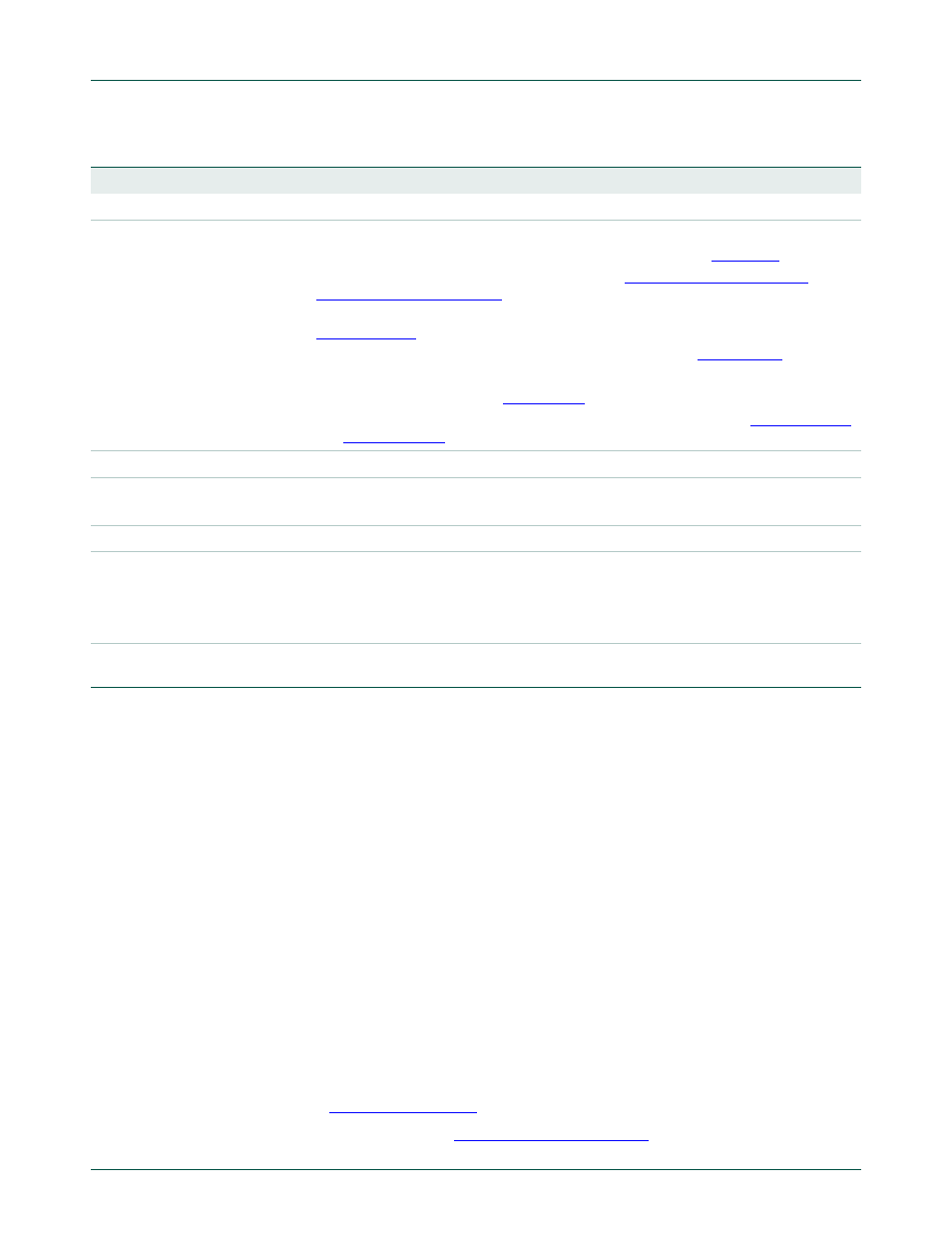

Revision history

Rev

Date

Description

04

20090826

LPC24XX user manual release.

Modifications:

•

Memory size for LPC2458 external SRAM memory corrected in

.

•

Deep power-down mode functionality added (see

and

).

•

Register containing device revision added (implemented starting with revision C, see

).

•

XTAL1 input selection and PCB layout guidelines added (see

).

•

Editorial updates throughout the user manual.

•

•

UART fractional baud rate generator disabled in auto baud mode (see

03

20090115

LPC24XX user manual release.

Modifications:

Description of AHB1 and AHB2 configuration registers updated.

02

20081219

LPC24XX user manual release.

Modifications:

•

Added parts LPC2420.

•

Editorial updates.

•

AHB1 and AHB2 configuration registers added.

01

20080718

Initial LPC24XX user manual release. Replaces all draft versions UM10237_1.00 to

UM10237_1.05.