Table 20–472, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 547

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

547 of 792

NXP Semiconductors

UM10237

Chapter 20: LPC24XX SSP interface SSP0/1

6.3 SSPn Data Register (SSP0DR - 0xE006 8008, SSP1DR - 0xE003 0008)

Software can write data to be transmitted to this register, and read data that has been

received.

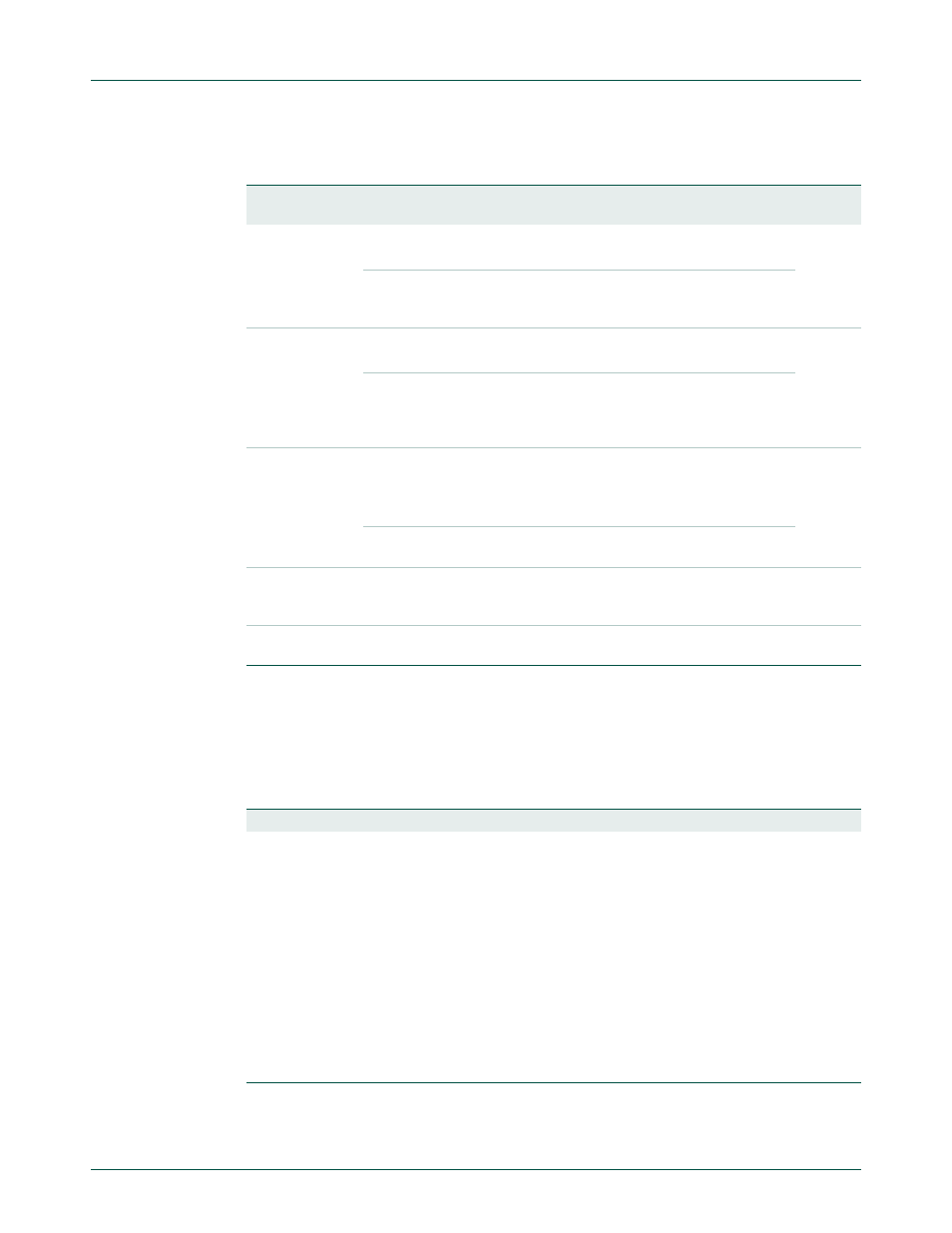

Table 472: SSPn Control Register 1 (SSP0CR1 - address 0xE006 8004, SSP1CR1 -

0xE003 0004) bit description

Bit

Symbol

Value

Description

Reset

Value

0

LBM

0

Loop Back Mode.

During normal operation.

0

1

Serial input is taken from the serial output (MOSI or MISO)

rather than the serial input pin (MISO or MOSI

respectively).

1

SSE

0

SSP Enable.

The SSP controller is disabled.

0

1

The SSP controller will interact with other devices on the

serial bus. Software should write the appropriate control

information to the other SSP registers and interrupt

controller registers, before setting this bit.

2

MS

0

Master/Slave Mode.This bit can only be written when the

SSE bit is 0.

The SSP controller acts as a master on the bus, driving the

SCLK, MOSI, and SSEL lines and receiving the MISO line.

0

1

The SSP controller acts as a slave on the bus, driving

MISO line and receiving SCLK, MOSI, and SSEL lines.

3

SOD

Slave Output Disable. This bit is relevant only in slave

mode (MS = 1). If it is 1, this blocks this SSP controller

from driving the transmit data line (MISO).

0

7:4

-

Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Table 473: SSPn Data Register (SSP0DR - address 0xE006 8008, SSP1DR - 0xE003 0008) bit

description

Bit

Symbol

Description

Reset Value

15:0

DATA

Write:

software can write data to be sent in a future frame to this

register whenever the TNF bit in the Status register is 1,

indicating that the Tx FIFO is not full. If the Tx FIFO was

previously empty and the SSP controller is not busy on the bus,

transmission of the data will begin immediately. Otherwise the

data written to this register will be sent as soon as all previous

data has been sent (and received). If the data length is less than

16 bits, software must right-justify the data written to this register.

Read:

software can read data from this register whenever the

RNE bit in the Status register is 1, indicating that the Rx FIFO is

not empty. When software reads this register, the SSP controller

returns data from the least recent frame in the Rx FIFO. If the

data length is less than 16 bits, the data is right-justified in this

field with higher order bits filled with 0s.

0x0000