Table 18–424, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 485

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

485 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

8.6 Bus Timing Register (CAN1BTR - 0xE004 4014, CAN2BTR -

0xE004 8014)

This register controls how various CAN timings are derived from the APB clock. It defines

the values of the Baud Rate Prescaler (BRP) and the Synchronization Jump Width (SJW).

Furthermore, it defines the length of the bit period, the location of the sample point and the

number of samples to be taken at each sample point. It can be read at any time but can

only be written if the RM bit in CANmod is 1.

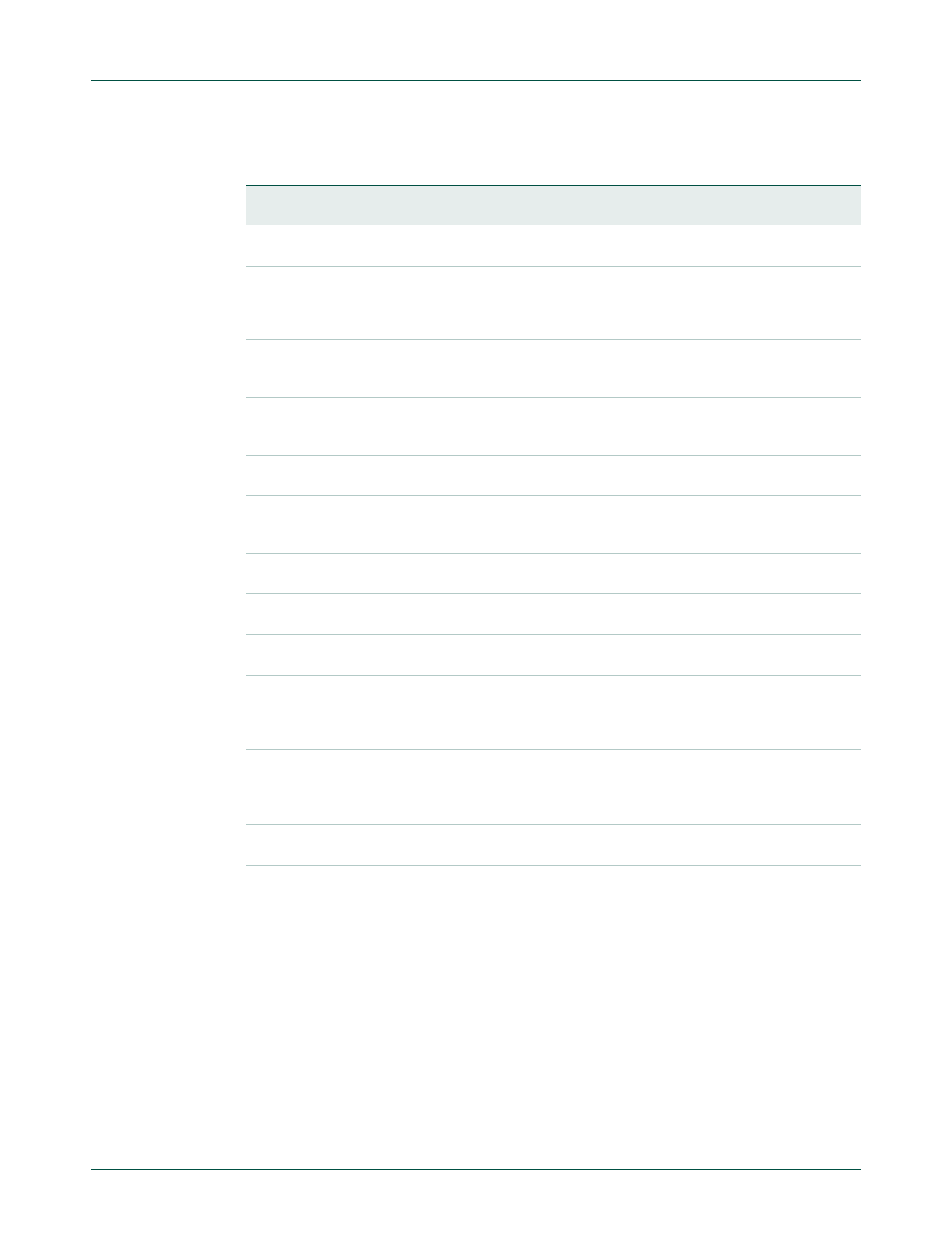

Table 424. Interrupt Enable Register (CAN1IER - address 0xE004 4010, CAN2IER - address

0xE004 8010) bit description

Bit

Symbol Function

Reset

Value

RM

Set

0

RIE

Receiver Interrupt Enable. When the Receive Buffer Status is 'full',

the CAN Controller requests the respective interrupt.

0

X

1

TIE1

Transmit Interrupt Enable for Buffer1. When a message has been

successfully transmitted out of TXB1 or Transmit Buffer 1 is

accessible again (e.g. after an Abort Transmission command), the

CAN Controller requests the respective interrupt.

0

X

2

EIE

Error Warning Interrupt Enable. If the Error or Bus Status change

(see Status Register), the CAN Controller requests the respective

interrupt.

0

X

3

DOIE

Data Overrun Interrupt Enable. If the Data Overrun Status bit is

set (see Status Register), the CAN Controller requests the

respective interrupt.

0

X

4

WUIE

Wake-Up Interrupt Enable. If the sleeping CAN controller wakes

up, the respective interrupt is requested.

0

X

5

EPIE

Error Passive Interrupt Enable. If the error status of the CAN

Controller changes from error active to error passive or vice versa,

the respective interrupt is requested.

0

X

6

ALIE

Arbitration Lost Interrupt Enable. If the CAN Controller has lost

arbitration, the respective interrupt is requested.

0

X

7

BEIE

Bus Error Interrupt Enable. If a bus error has been detected, the

CAN Controller requests the respective interrupt.

0

X

8

IDIE

ID Ready Interrupt Enable. When a CAN identifier has been

received, the CAN Controller requests the respective interrupt.

0

X

9

TIE2

Transmit Interrupt Enable for Buffer2. When a message has been

successfully transmitted out of TXB2 or Transmit Buffer 2 is

accessible again (e.g. after an Abort Transmission command), the

CAN Controller requests the respective interrupt.

0

X

10

TIE3

Transmit Interrupt Enable for Buffer3. When a message has been

successfully transmitted out of TXB3 or Transmit Buffer 3 is

accessible again (e.g. after an Abort Transmission command), the

CAN Controller requests the respective interrupt.

0

X

31:11

-

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA