Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 89

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

89 of 792

NXP Semiconductors

UM10237

Chapter 5: LPC24XX External Memory Controller (EMC)

[1]

The SDRAM column and row width and number of banks are computed automatically from the address

mapping.

[2]

The buffers must be disabled during SDRAM and SyncFlash initialization. They must also be disabled when

performing SyncFlash commands. The buffers must be enabled during normal operation.

Address mappings that are not shown in

are reserved.

Table 86.

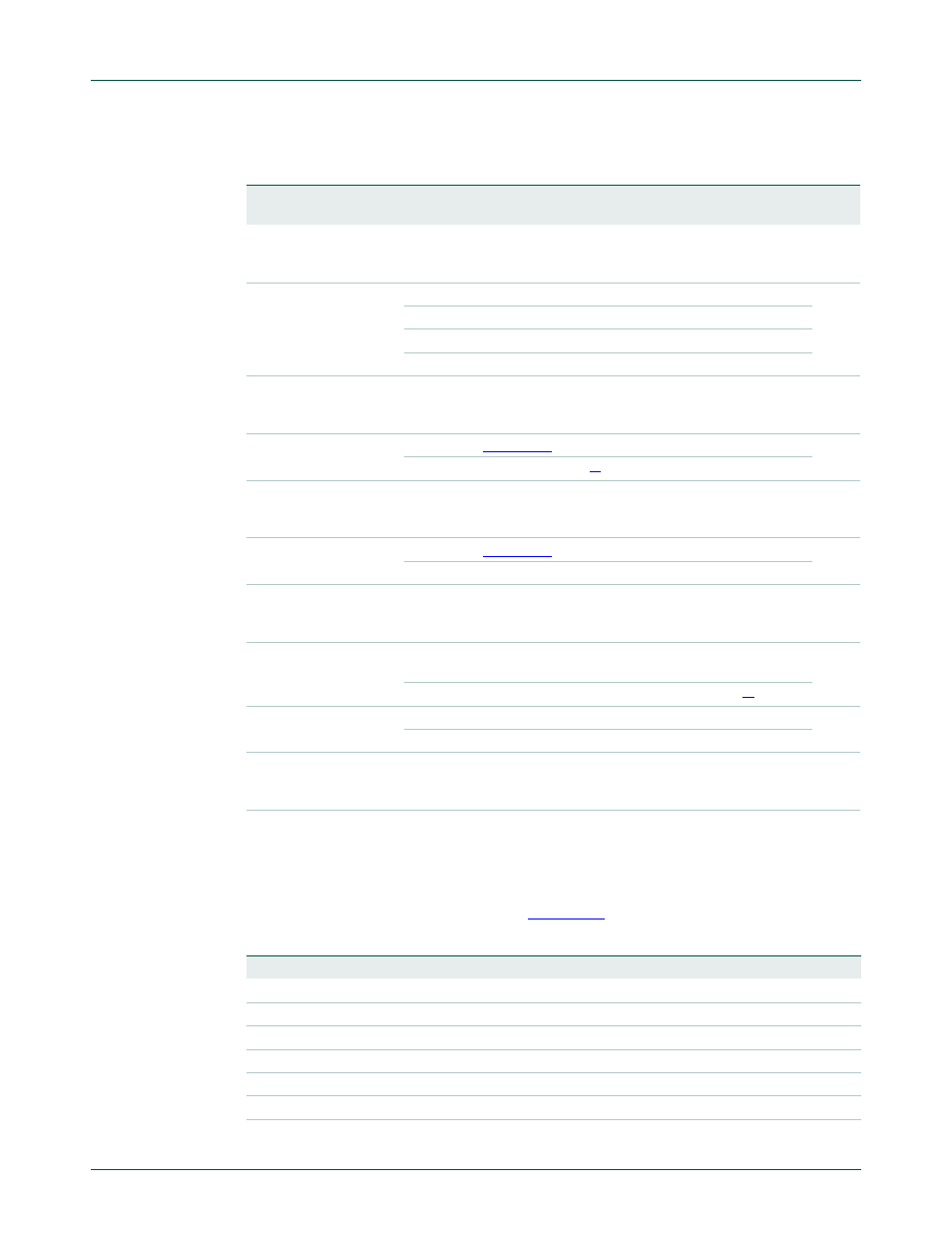

Dynamic Memory Configuration registers (EMCDynamicConfig0-3 - address

0xFFE0 8100, 0xFFE0 8120, 0xFFE0 8140, 0xFFE0 8160) bit description

Bit

Symbol

Value Description

Reset

Value

2:0

-

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

4:3

Memory device

(MD)

00

SDRAM (POR reset value).

00

01

Low-power SDRAM.

10

Micron SyncFlash.

11

Reserved.

6:5

-

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

12:7

Address

mapping (AM)

0

0

000000 = reset value.

13

-

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

14

Address

mapping (AM)

0

0

0 = reset value.

18:15 -

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

19

Buffer enable

(B)

0

Buffer disabled for accesses to this chip select (POR

reset value).

1

Buffer enabled for accesses to this chip select.

20

Write protect (P) 0

Writes not protected (POR reset value).

0

1

Writes protected.

31:21 -

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Table 87.

Address mapping

14

12

11:9 8:7

Description

16 bit external bus high-performance address mapping (Row, Bank, Column)

0

0

000

00

16 MB (2Mx8), 2 banks, row length = 11, column length = 9

0

0

000

01

16 MB (1Mx16), 2 banks, row length = 11, column length = 8

0

0

001

00

64 MB (8Mx8), 4 banks, row length = 12, column length = 9

0

0

001

01

64 MB (4Mx16), 4 banks, row length = 12, column length = 8

0

0

010

00

128 MB (16Mx8), 4 banks, row length = 12, column length = 10

0

0

010

01

128 MB (8Mx16), 4 banks, row length = 12, column length = 9