Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 437

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

437 of 792

NXP Semiconductors

UM10237

Chapter 16: LPC24XX UART0/2/3

4.11 IrDA Control Register for UART3 Only (U3ICR - 0xE007 C024)

The IrDA Control Register enables and configures the IrDA mode for UART3 only. The

value of U3ICR should not be changed while transmitting or receiving data, or data loss or

corruption may occur.

The PulseDiv bits in U3ICR are used to select the pulse width when the fixed pulse width

mode is used in IrDA mode (IrDAEn = 1 and FixPulseEn = 1). The value of these bits

should be set so that the resulting pulse width is at least 1.63 µs.

shows the

possible pulse widths.

4.12 UARTn Fractional Divider Register (U0FDR - 0xE000 C028, U2FDR -

0xE007 8028, U3FDR - 0xE007 C028)

The UART0/2/3 Fractional Divider Register (U0/2/3FDR) controls the clock pre-scaler for

the baud rate generation and can be read and written at the user’s discretion. This

pre-scaler takes the APB clock and generates an output clock according to the specified

fractional requirements.

Important: If the fractional divider is active (DIVADDVAL > 0) and DLM = 0, the value of

the DLL register must be 3 or greater.

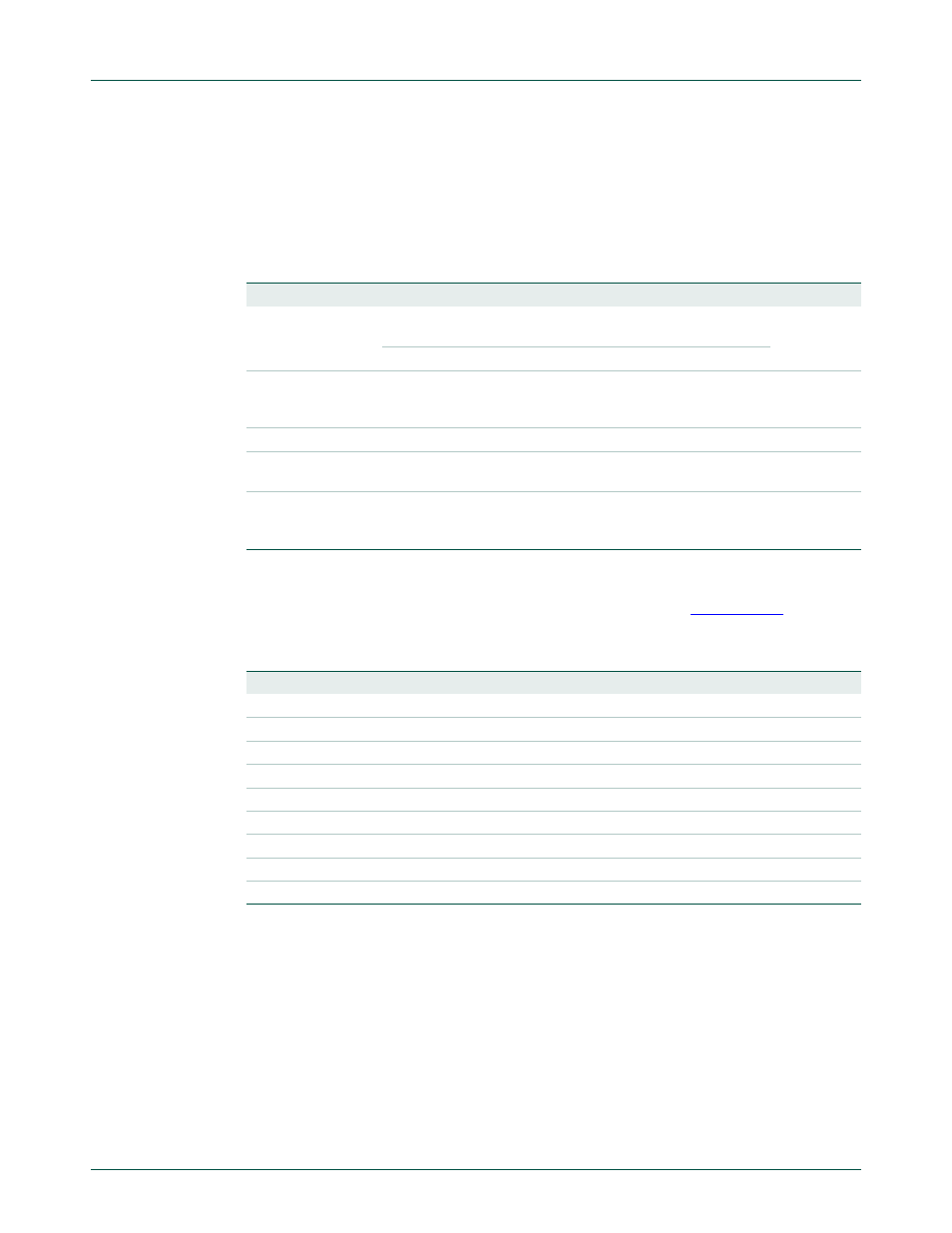

Table 390. IrDA Control Register for UART3 only (U3ICR - address 0xE007 C024) bit

description

Bit

Symbol

Value Description

Reset value

0

IrDAEn

0

IrDA mode on UART3 is disabled, UART3 acts as a

standard UART.

0

1

IrDA mode on UART3 is enabled.

1

IrDAInv

When 1, the serial input is inverted. This has no effect

on the serial output. When 0, the serial input is not

inverted.

0

2

FixPulseEn

When 1, enabled IrDA fixed pulse width mode.

0

5:3

PulseDiv

Configures the pulse when FixPulseEn = 1. See text

below for details.

0

31:6

-

NA

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is

not defined.

0

Table 391. IrDA Pulse Width

FixPulseEn

PulseDiv

IrDA Transmitter Pulse width (µs)

0

x

3 / (16

× baud rate)

1

0

2

× T

PCLK

1

1

4

× T

PCLK

1

2

8

× T

PCLK

1

3

16

× T

PCLK

1

4

32

× T

PCLK

1

5

64

× T

PCLK

1

6

128

× T

PCLK

1

7

256

× T

PCLK