1 power control register (mci power - 0xe008 c000), 2 clock control register (mciclock - 0xe008 c004), Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 564

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

564 of 792

NXP Semiconductors

UM10237

Chapter 21: LPC24XX SD/MMC card interface

[1]

Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

6.1 Power Control Register (MCI Power - 0xE008 C000)

The MCIPower register controls an external power supply. Power can be switched on and

off, and adjust the output voltage.

shows the bit assignment of the

MCIPower register.

The active level of the MCIPWR (Power Supply Enable) pin can be selected by bit 3 of the

SCS register (see

Section 3–7.1 “System Controls and Status register (SCS - 0xE01F

C1A0)” on page 36

for details).

When the external power supply is switched on, the software first enters the power-up

phase, and waits until the supply output is stable before moving to the power-on phase.

During the power-up phase, MCIPWR is set HIGH. The card bus outlets are disabled

during both phases.

Note: After a data write, data cannot be written to this register for three MCLK clock

periods plus two PCLK clock periods.

6.2 Clock Control Register (MCIClock - 0xE008 C004)

The MCIClock register controls the MCICLK output.

shows the bit

assignment of the clock control register.

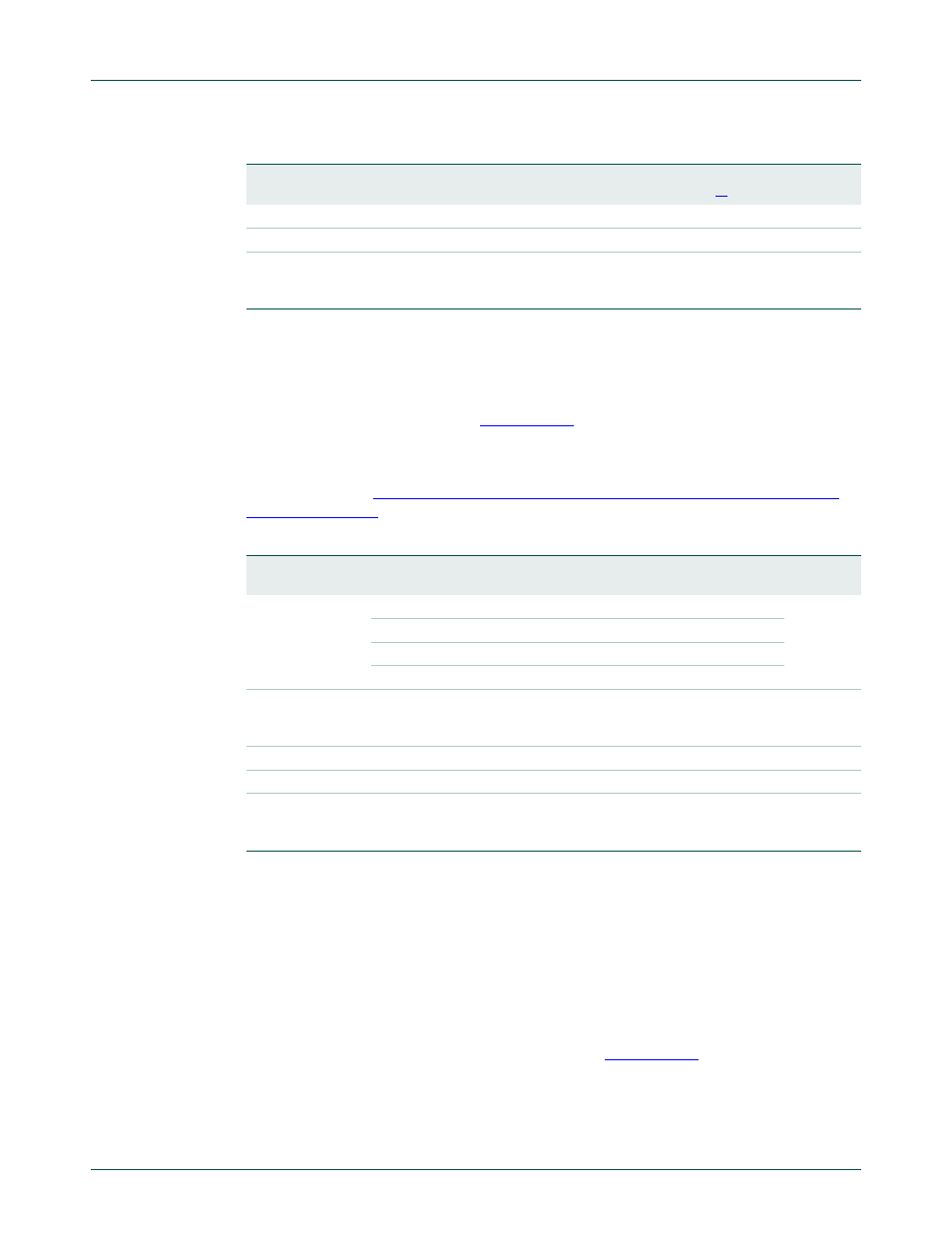

MCIMask0

Interrupt 0 mask register.

R/W

22

0x000000

0xE008 C03C

MCIFifoCnt

FIFO Counter.

RO

15

0x0000

0xE008 C048

MCIFIFO

Data FIFO Register.

R/W

32

0x00000000 0xE008 C080

to

0xE008 C0BC

Table 490. Summary of MCI registers

Name

Description

Access Width Reset

Value

[1]

Address

Table 491: Power Control register (MCIPower - address 0xE008 C000) bit description

Bit

Symbol

Value Description

Reset

Value

1:0

Ctrl

00

Power-off

00

01

Reserved

10

Power-up

11

Power-on

5:2

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

6

OpenDrain

MCICMD output control.

0

7

Rod

Rod control.

0

31:8

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA