Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 584

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

584 of 792

NXP Semiconductors

UM10237

Chapter 22: LPC24XX I

2

C interfaces I

2

C0/1/2

8.2 I

2

C Control Clear Register (I2C[0/1/2]CONCLR: 0xE001 C018,

0xE005 C018, 0xE008 0018)

The I2CONCLR registers control clearing of bits in the I2CON register that controls

operation of the I

2

C interface. Writing a one to a bit of this register causes the

corresponding bit in the I

2

C control register to be cleared. Writing a zero has no effect.

AAC is the Assert Acknowledge Clear bit. Writing a 1 to this bit clears the AA bit in the

I2CONSET register. Writing 0 has no effect.

SIC is the I

2

C Interrupt Clear bit. Writing a 1 to this bit clears the SI bit in the I2CONSET

register. Writing 0 has no effect.

STAC is the Start flag Clear bit. Writing a 1 to this bit clears the STA bit in the I2CONSET

register. Writing 0 has no effect.

I2ENC is the I

2

C Interface Disable bit. Writing a 1 to this bit clears the I2EN bit in the

I2CONSET register. Writing 0 has no effect.

8.3 I

2

C Status Register (I2C[0/1/2]STAT - 0xE001 C004, 0xE005 C004,

0xE008 0004)

Each I

2

C Status register reflects the condition of the corresponding I

2

C interface. The I

2

C

Status register is Read-Only.

The three least significant bits are always 0. Taken as a byte, the status register contents

represent a status code. There are 26 possible status codes. When the status code is

0xF8, there is no relevant information available and the SI bit is not set. All other 25 status

codes correspond to defined I

2

C states. When any of these states entered, the SI bit will

be set. For a complete list of status codes, refer to tables from

to

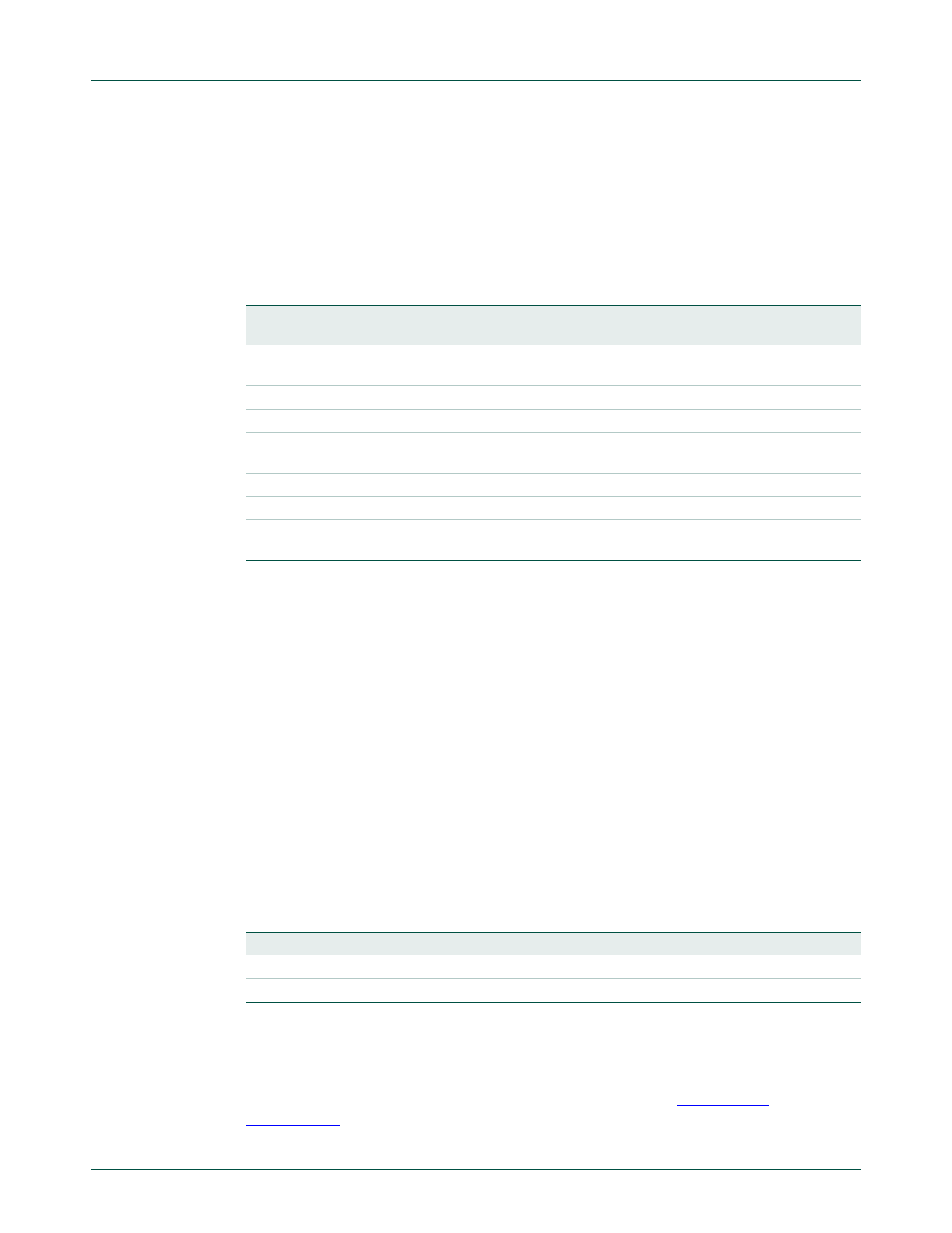

Table 514. I

2

C Control Set Register (I2C[0/1/2]CONCLR - addresses 0xE001 C018,

0xE005 C018, 0xE008 0018) bit description

Bit Symbol

Description

Reset

Value

1:0 -

Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

2

AAC

Assert acknowledge Clear bit.

3

SIC

I

2

C interrupt Clear bit.

0

4

-

Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

5

STAC

START flag Clear bit.

0

6

I2ENC

I

2

C interface Disable bit.

0

7

-

Reserved. User software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 515. I

2

C Status Register (I2C[0/1/2]STAT - addresses 0xE001 C004, 0xE005 C004,

0xE008 0004) bit description

Bit Symbol

Description

Reset Value

2:0 -

These bits are unused and are always 0.

0

7:3 Status

These bits give the actual status information about the I

2

C interface. 0x1F