Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 392

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

392 of 792

NXP Semiconductors

UM10237

Chapter 14: LPC24XX USB Host controller

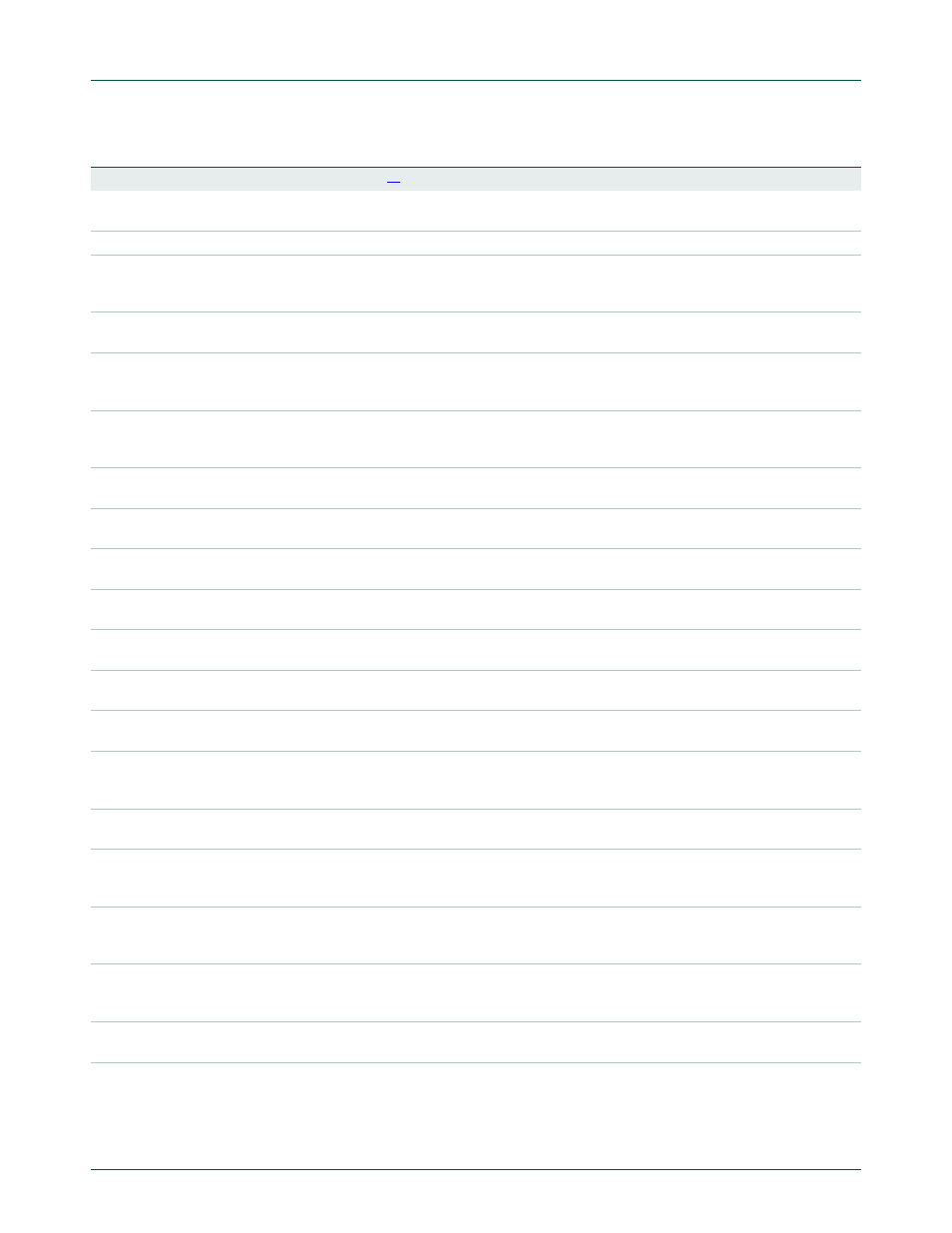

Table 360. USB Host register address definitions

Name

Address

Function

Reset value

HcRevision

0xFFE0 C000

R

BCD representation of the version of the HCI

specification that is implemented by the Host Controller.

0x10

HcControl

0xFFE0 C004

R/W

Defines the operating modes of the HC.

0x0

HcCommandStatus

0xFFE0 C008

R/W

This register is used to receive the commands from the

Host Controller Driver (HCD). It also indicates the status

of the HC.

0x0

HcInterruptStatus

0xFFE0 C00C

R/W

Indicates the status on various events that cause

hardware interrupts by setting the appropriate bits.

0x0

HcInterruptEnable

0xFFE0 C010

R/W

Controls the bits in the HcInterruptStatus register and

indicates which events will generate a hardware

interrupt.

0x0

HcInterruptDisable

0xFFE0 C014

R/W

The bits in this register are used to disable

corresponding bits in the HCInterruptStatus register and

in turn disable that event leading to hardware interrupt.

0x0

HcHCCA

0xFFE0 C018

R/W

Contains the physical address of the host controller

communication area.

0x0

HcPeriodCurrentED

0xFFE0 C01C

R

Contains the physical address of the current isochronous

or interrupt endpoint descriptor.

0x0

HcControlHeadED

0xFFE0 C020

R/W

Contains the physical address of the first endpoint

descriptor of the control list.

0x0

HcControlCurrentED

0xFFE0 C024

R/W

Contains the physical address of the current endpoint

descriptor of the control list

0x0

HcBulkHeadED

0xFFE0 C028

R/W

Contains the physical address of the first endpoint

descriptor of the bulk list.

0x0

HcBulkCurrentED

0xFFE0 C02C

R/W

Contains the physical address of the current endpoint

descriptor of the bulk list.

0x0

HcDoneHead

0xFFE0 C030

R

Contains the physical address of the last transfer

descriptor added to the ‘Done’ queue.

0x0

HcFmInterval

0xFFE0 C034

R/W

Defines the bit time interval in a frame and the full speed

maximum packet size which would not cause an

overrun.

0x2EDF

HcFmRemaining

0xFFE0 C038

R

A 14-bit counter showing the bit time remaining in the

current frame.

0x0

HcFmNumber

0xFFE0 C03C

R

Contains a 16-bit counter and provides the timing

reference among events happening in the HC and the

HCD.

0x0

HcPeriodicStart

0xFFE0 C040

R/W

Contains a programmable 14-bit value which determines

the earliest time HC should start processing a periodic

list.

0x0

HcLSThreshold

0xFFE0 C044

R/W

Contains 11-bit value which is used by the HC to

determine whether to commit to transfer a maximum of

8-byte LS packet before EOF.

0x628h

HcRhDescriptorA

0xFFE0 C048

R/W

First of the two registers which describes the

characteristics of the root hub.

0xFF000902

HcRhDescriptorB

0xFFE0 C04C

R/W

Second of the two registers which describes the

characteristics of the Root Hub.

0x60000h