Brown-out detection, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 39

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

39 of 792

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

[1]

The state of this bit is preserved through a software reset, and only a POR or a BOD event will reset it to its default value.

4.

Brown-out detection

The LPC2400 includes 2-stage monitoring of the voltage on the V

DD(DCDC)(3V3)

pins. If this

voltage falls below 2.95 V, the Brown-Out Detector (BOD) asserts an interrupt signal to

the Vectored Interrupt Controller. This signal can be enabled for interrupt in the Interrupt

Enable Register in the VIC (see

Section 7–3.4 “Interrupt Enable Register (VICIntEnable -

) in order to cause a CPU interrupt; if not, software can monitor the signal

by reading the Raw Interrupt Status Register (see

Section 7–3.3 “Raw Interrupt Status

Register (VICRawIntr - 0xFFFF F008)”

The second stage of low-voltage detection asserts Reset to inactivate the LPC2400 when

the voltage on the V

DD(DCDC)(3V3)

pins falls below 2.65 V. This Reset prevents alteration of

the flash as operation of the various elements of the chip would otherwise become

unreliable due to low voltage. The BOD circuit maintains this reset down below 1 V, at

which point the Power-On Reset circuitry maintains the overall Reset.

Both the 2.95 V and 2.65 V thresholds include some hysteresis. In normal operation, this

hysteresis allows the 2.95 V detection to reliably interrupt, or a regularly-executed event

loop to sense the condition.

But when Brown-Out Detection is enabled to bring the LPC2400 out of Power-Down mode

(which is itself not a guaranteed operation -- see

Section 4–3.4.7 “Power Mode Control

register (PCON - 0xE01F C0C0)”

), the supply voltage may recover from a transient before

the Wakeup Timer has completed its delay. In this case, the net result of the transient

BOD is that the part wakes up and continues operation after the instructions that set

Power-Down Mode, without any interrupt occurring and with the BOD bit in the RSID

being 0. Since all other wakeup conditions have latching flags (see

“External Interrupt flag register (EXTINT - 0xE01F C140)”

and

), a wakeup

of this type, without any apparent cause, can be assumed to be a Brown-Out that has

gone away.

5

OSCEN

Main oscillator enable.

R/W

0

0

The main oscillator is disabled.

1

The main oscillator is enabled, and will start up if the correct external

circuitry is connected to the XTAL1 and XTAL2 pins.

6

OSCSTAT

Main oscillator status.

RO

0

0

The main oscillator is not ready to be used as a clock source.

1

The main oscillator is ready to be used as a clock source. The main

oscillator must be enabled via the OSCEN bit.

31:7 -

-

Reserved. User software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

-

NA

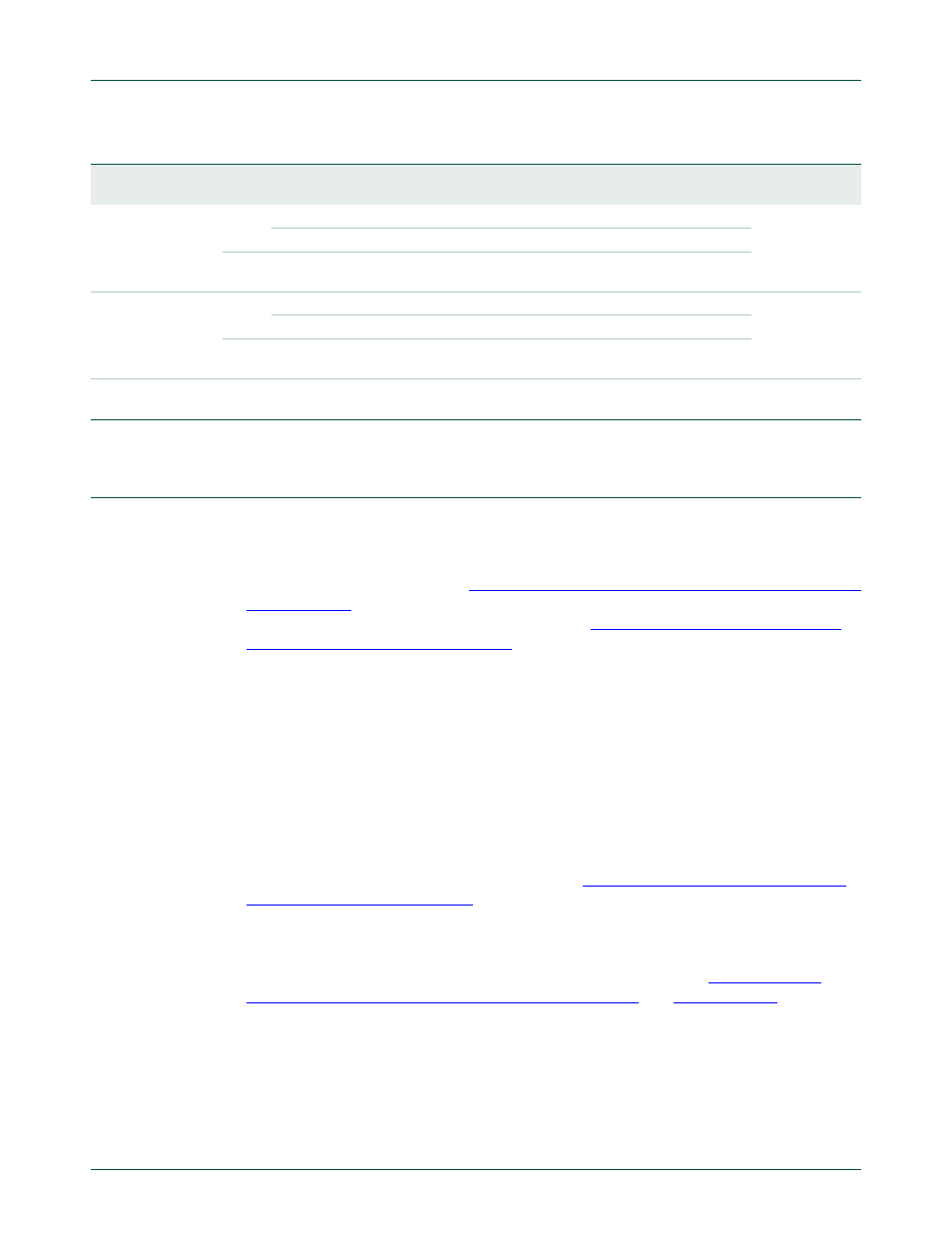

Table 38.

System Controls and Status register (SCS - address 0xE01F C1A0) bit description

Bit

Symbol

Value Description

Access Reset

value