3 transmit fifo register (i2stxfifo - 0xe008 8008), 4 receive fifo register (i2srxfifo - 0xe008 800c), Table 23–533 – NXP Semiconductors LPC24XX UM10237 User Manual

Page 615: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

615 of 792

NXP Semiconductors

UM10237

Chapter 23: LPC24XX I

2

S interface

5.3 Transmit FIFO Register (I2STXFIFO - 0xE008 8008)

The I2STXFIFO register provides access to the transmit FIFO. The function of bits in

I2STXFIFO are shown in

.

5.4 Receive FIFO Register (I2SRXFIFO - 0xE008 800C)

The I2SRXFIFO register provides access to the receive FIFO. The function of bits in

I2SRXFIFO are shown in

.

5.5 Status Feedback Register (I2SSTATE - 0xE008 8010)

The I2SSTATE register provides status information about the I2S interface. The meaning

of bits in I2SSTATE are shown in

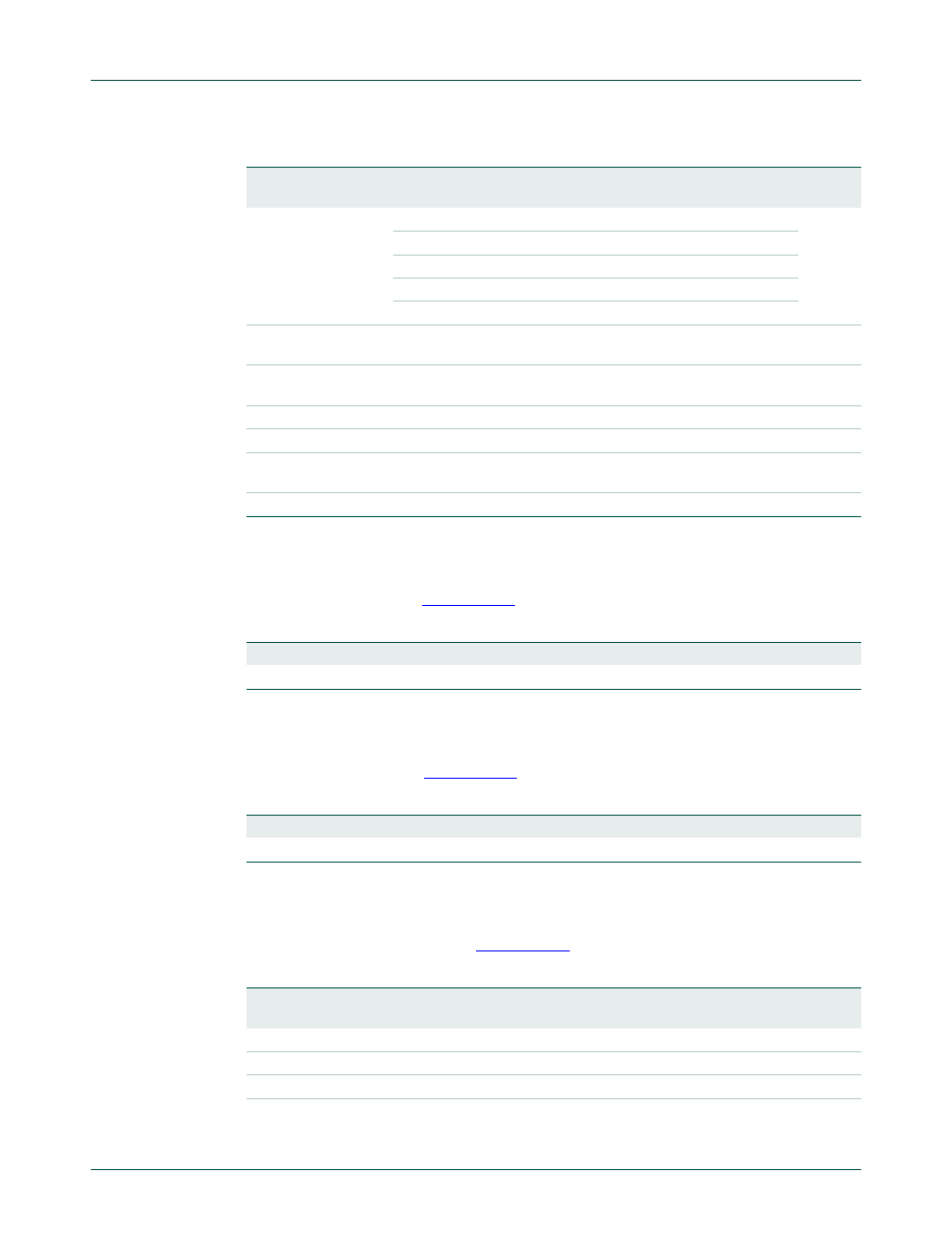

Table 533: Digital Audio Input register (I2SDAI - address 0xE008 8004) bit description

Bit

Symbol

Value Description

Reset

Value

1:0

wordwidth

Selects the number of bytes in data as follows:

01

00

8 bit data

01

16 bit data

10

Reserved, do not use this setting

11

32 bit data

2

mono

When one, data is of monaural format. When zero, the

data is in stereo format.

0

3

stop

Disables accesses on FIFOs, places the transmit

channel in mute mode.

0

4

reset

Asynchronously reset the transmit channel and FIFO.

0

5

ws_sel

When 0 master mode, when 1 slave mode.

1

14:6

ws_halfperiod

Word select half period minus one, i.e. WS 64clk period

-> ws_halfperiod = 31.

0x1F

15

Unused

Unused.

1

Table 534: Transmit FIFO register (I2STXFIFO - address 0xE008 8008) bit description

Bit

Symbol

Description

Reset Value

31:0

I2STXFIFO

8

×

32 bits transmit FIFO.

Level = 0

Table 535: Receive FIFO register (I2RXFIFO - address 0xE008 800C) bit description

Bit

Symbol

Description

Reset Value

31:0

I2SRXFIFO

8

×

32 bits transmit FIFO.

level = 0

Table 536: Status Feedback register (I2SSTATE - address 0xE008 8010) bit description

Bit

Symbol

Description

Reset

Value

0

irq

This bit reflects the presence of Receive Interrupt or Transmit Interrupt. 0

1

dmareq1

This bit reflects the presence of Receive or Transmit DMA Request 1.

0

2

dmareq2

This bit reflects the presence of Receive or Transmit DMA Request 2.

0

7:3

Unused

Unused.

0