Section 7–3.3 “raw interrupt status, Register (vicrawintr - 0xffff f008), Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 112

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 20 August 2009

112 of 792

NXP Semiconductors

UM10237

Chapter 7: LPC24XX Vectored Interrupt Controller (VIC)

[1]

Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

The following section describes the VIC registers in the order in which they are used in the

VIC logic, from those closest to the interrupt request inputs to those most abstracted for

use by software. For most people, this is also the best order to read about the registers

when learning the VIC.

3.1 Software Interrupt Register (VICSoftInt - 0xFFFF F018)

The VICSoftInt register is used to generate software interrupts. The contents of this

register are ORed with the 32 interrupt requests from the various peripherals, before any

other logic is applied.

3.2 Software Interrupt Clear Register (VICSoftIntClear - 0xFFFF F01C)

The VICSoftIntClear register is a ’Write Only’ register. This register allows software to

clear one or more bits in the Software Interrupt register, without having to first read it.

3.3 Raw Interrupt Status Register (VICRawIntr - 0xFFFF F008)

This is a read only register. This register reads out the state of the 32 interrupt requests

and software interrupts, regardless of enabling or classification.

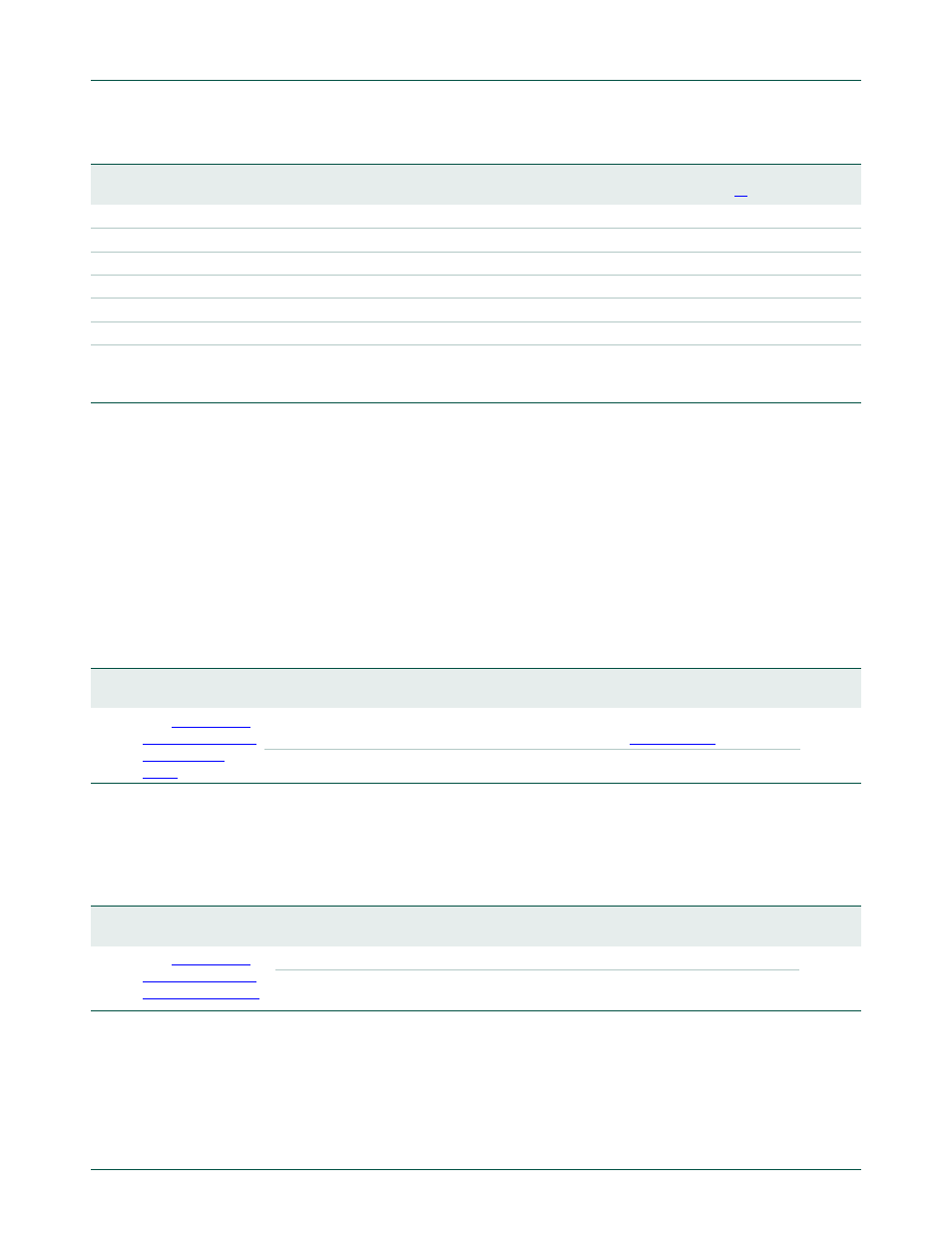

VICVectPriority26

Vector priority 26 register.

R/W

0xF

0xFFFF F268

VICVectPriority27

Vector priority 27 register.

R/W

0xF

0xFFFF F26C

VICVectPriority28

Vector priority 28 register.

R/W

0xF

0xFFFF F270

VICVectPriority29

Vector priority 29 register.

R/W

0xF

0xFFFF F274

VICVectPriority30

Vector priority 30 register.

R/W

0xF

0xFFFF F278

VICVectPriority31

Vector priority 31 register.

R/W

0xF

0xFFFF F27C

VICAddress

Vector address register. When an IRQ interrupt occurs, the

Vector Address Register holds the address of the currently

active interrupt.

R/W

0

0xFFFF FF00

Table 102. Summary of VIC registers

Name

Description

Access

Reset

value

[1]

Address

Table 103. Software Interrupt register (VICSoftInt - address 0xFFFF F018) bit description

Bit

Symbol

Value

Description

Reset

value

31:0

See

“Interrupt sources

bit allocation

table”

0

Do not force the interrupt request with this bit number. Writing zeroes to bits

in VICSoftInt has no effect, see VICSoftIntClear (

0

1

Force the interrupt request with this bit number.

Table 104. Software Interrupt Clear register (VICSoftIntClear - address 0xFFFF F01C) bit description

Bit

Symbol

Value

Description

Reset

value

31:0

“Interrupt sources

bit allocation table”

.

0

Writing a 0 leaves the corresponding bit in VICSoftInt unchanged.

0

1

Writing a 1 clears the corresponding bit in the Software Interrupt register,

removing any interrupt that may have been generated by that bit.