Boot process flowchart, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 680

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

680 of 792

NXP Semiconductors

UM10237

Chapter 30: LPC24XX Flash memory programming firmware

6.

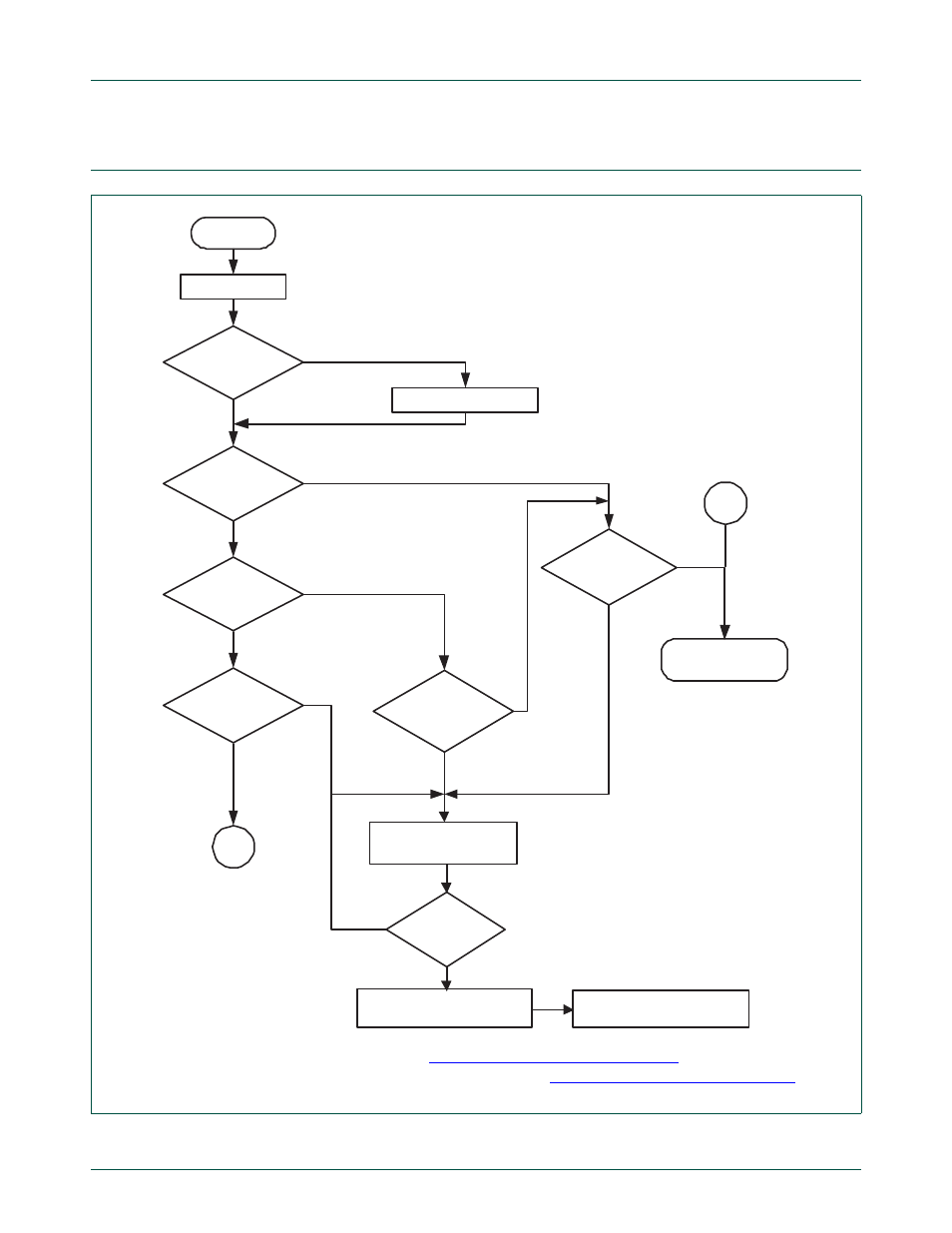

Boot process flowchart

(1) For details on handling the crystal frequency, see

Section 30–10.8 “Reinvoke ISP” on page 695

(2) For details on available ISP commands based on the CRP settings see

Section 30–8 “Code Read Protection (CRP)”

Fig 139. Boot process flowchart

WATCHDOG

FLAG SET?

CRP1/2/3 ENABLED?

yes

no

INITIALIZE

RESET

ENABLE DEBUG

yes

RUN ISP COMMAND

HANDLER

2

RECEIVE CRYSTAL

FREQUENCY

1

no

AUTO-BAUD

SUCCESSFUL?

yes

RUN AUTO-BAUD

USER CODE

VALID?

yes

no

CRP3 ENABLED?

Enter ISP

MODE?

(P2.10=LOW)

USER CODE VALID?

yes

yes

no

yes

no

no

A

A

EXECUTE INTERNAL

USER CODE