Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 477

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

477 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

[1]

- Setting the command bits TR and AT simultaneously results in transmitting a message once. No re-transmission will be performed in

case of an error or arbitration lost (single shot transmission).

- Setting the command bits SRR and TR simultaneously results in sending the transmit message once using the self-reception feature.

No re-transmission will be performed in case of an error or arbitration lost.

- Setting the command bits TR, AT and SRR simultaneously results in transmitting a message once as described for TR and AT. The

moment the Transmit Status bit is set within the Status Register, the internal Transmission Request Bit is cleared automatically.

- Setting TR and SRR simultaneously will ignore the set SRR bit.

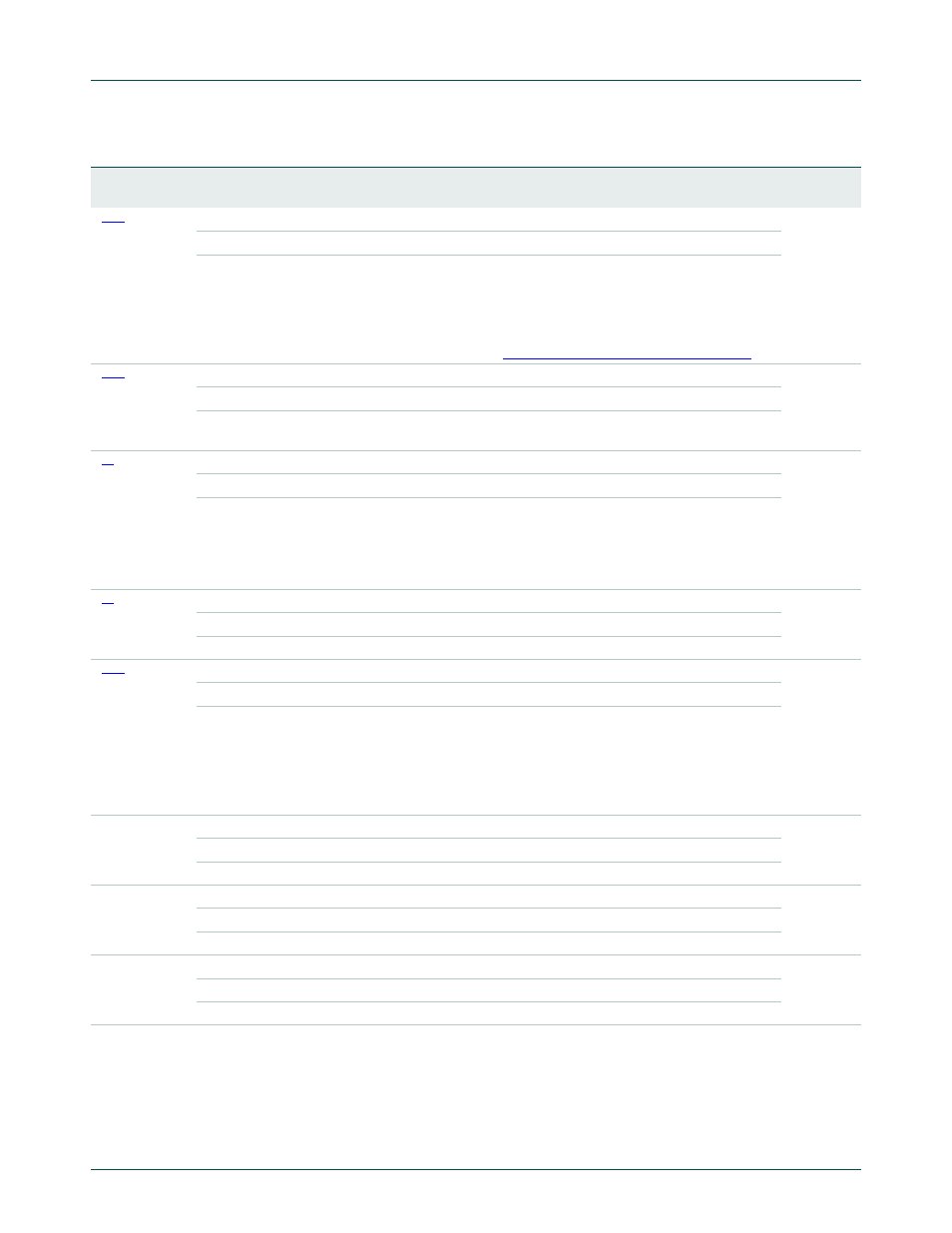

Table 421. Command Register (CAN1CMR - address 0xE004 4004, CAN2CMR - address 0xE004 8004) bit description

Bit

Symbol Value

Function

Reset

Value

RM

Set

TR

Transmission Request.

0

0

0 (absent)

No transmission request.

1 (present)

The message, previously written to the CANxTFI, CANxTID, and

optionally the CANxTDA and CANxTDB registers, is queued for

transmission from the selected Transmit Buffer. If at two or all three

of STB1, STB2 and STB3 bits are selected when TR=1 is written,

Transmit Buffer will be selected based on the chosen priority

scheme (for details see

Section 18–6.3 “Transmit Buffers (TXB)”

AT

Abort Transmission.

0

0

0 (no action)

Do not abort the transmission.

1 (present)

if not already in progress, a pending Transmission Request for the

selected Transmit Buffer is cancelled.

RRB

Release Receive Buffer.

0

0

0 (no action)

Do not release the receive buffer.

1 (released)

The information in the Receive Buffer (consisting of CANxRFS,

CANxRID, and if applicable the CANxRDA and CANxRDB registers)

is released, and becomes eligible for replacement by the next

received frame. If the next received frame is not available, writing

this command clears the RBS bit in the Status Register(s).

CDO

Clear Data Overrun.

0

0

0 (no action)

Do not clear the data overrun bit.

1 (clear)

The Data Overrun bit in Status Register(s) is cleared.

SRR

Self Reception Request.

0

0

0 (absent)

No self reception request.

1 (present)

The message, previously written to the CANxTFS, CANxTID, and

optionally the CANxTDA and CANxTDB registers, is queued for

transmission from the selected Transmit Buffer and received

simultaneously. This differs from the TR bit above in that the receiver

is not disabled during the transmission, so that it receives the

message if its Identifier is recognized by the Acceptance Filter.

5

STB1

Select Tx Buffer 1.

0

0

0 (not selected)

Tx Buffer 1 is not selected for transmission.

1 (selected)

Tx Buffer 1 is selected for transmission.

6

STB2

Select Tx Buffer 2.

0

0

0 (not selected)

Tx Buffer 2 is not selected for transmission.

1 (selected)

Tx Buffer 2 is selected for transmission.

7

STB3

Select Tx Buffer 3.

0

0

0 (not selected)

Tx Buffer 3 is not selected for transmission.

1 (selected)

Tx Buffer 3 is selected for transmission.