Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 496

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

496 of 792

NXP Semiconductors

UM10237

Chapter 18: LPC24XX CAN controllers CAN1/2

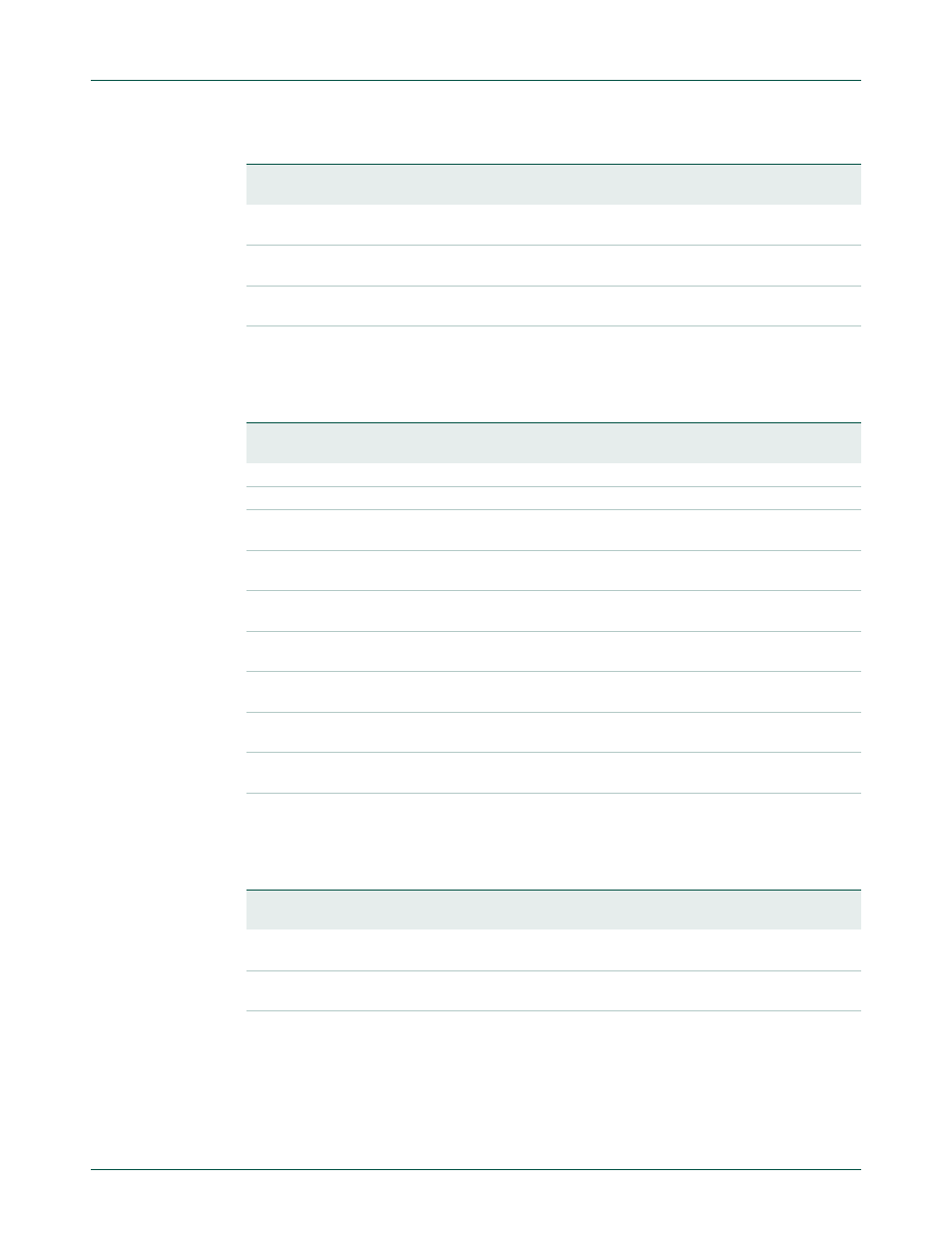

10.2 Central Receive Status Register (CANRxSR - 0xE004 0004)

10.3 Central Miscellaneous Status Register (CANMSR - 0xE004 0008)

16

TCS1

When 1, all requested transmissions have been completed successfully

by the CAN1 controller (same as TCS in CAN1GSR).

1

17:16 TCS2

When 1, all requested transmissions have been completed successfully

by the CAN2 controller (same as TCS in CAN2GSR).

1

31:18 -

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 438. Central Transit Status Register (CANTxSR - address 0xE004 0000) bit description

Bit

Symbol

Description

Reset

Value

Table 439. Central Receive Status Register (CANRxSR - address 0xE004 0004) bit

description

Bit

Symbol Description

Reset

Value

0

RS1

When 1, CAN1 is receiving a message (same as RS in CAN1GSR).

0

1

RS2

When 1, CAN2 is receiving a message (same as RS in CAN2GSR).

0

7:2

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

8

RB1

When 1, a received message is available in the CAN1 controller (same

as RBS in CAN1GSR).

0

9

RB2

When 1, a received message is available in the CAN2 controller (same

as RBS in CAN2GSR).

0

15:10 -

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

16

DOS1

When 1, a message was lost because the preceding message to CAN1

controller was not read out quickly enough (same as DOS in CAN1GSR).

0

17:16 DOS2

When 1, a message was lost because the preceding message to CAN2

controller was not read out quickly enough (same as DOS in CAN2GSR).

0

31:18 -

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 440. Central Miscellaneous Status Register (CANMSR - address 0xE004 0008) bit

description

Bit

Symbol Description

Reset

Value

0

E1

When 1, one or both of the CAN1 Tx and Rx Error Counters has reached

the limit set in the CAN1EWL register (same as ES in CAN1GSR)

0

1

E2

When 1, one or both of the CAN2 Tx and Rx Error Counters has reached

the limit set in the CAN2EWL register (same as ES in CAN2GSR)

0

7:2

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA