Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 76

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

76 of 792

NXP Semiconductors

UM10237

Chapter 5: LPC24XX External Memory Controller (EMC)

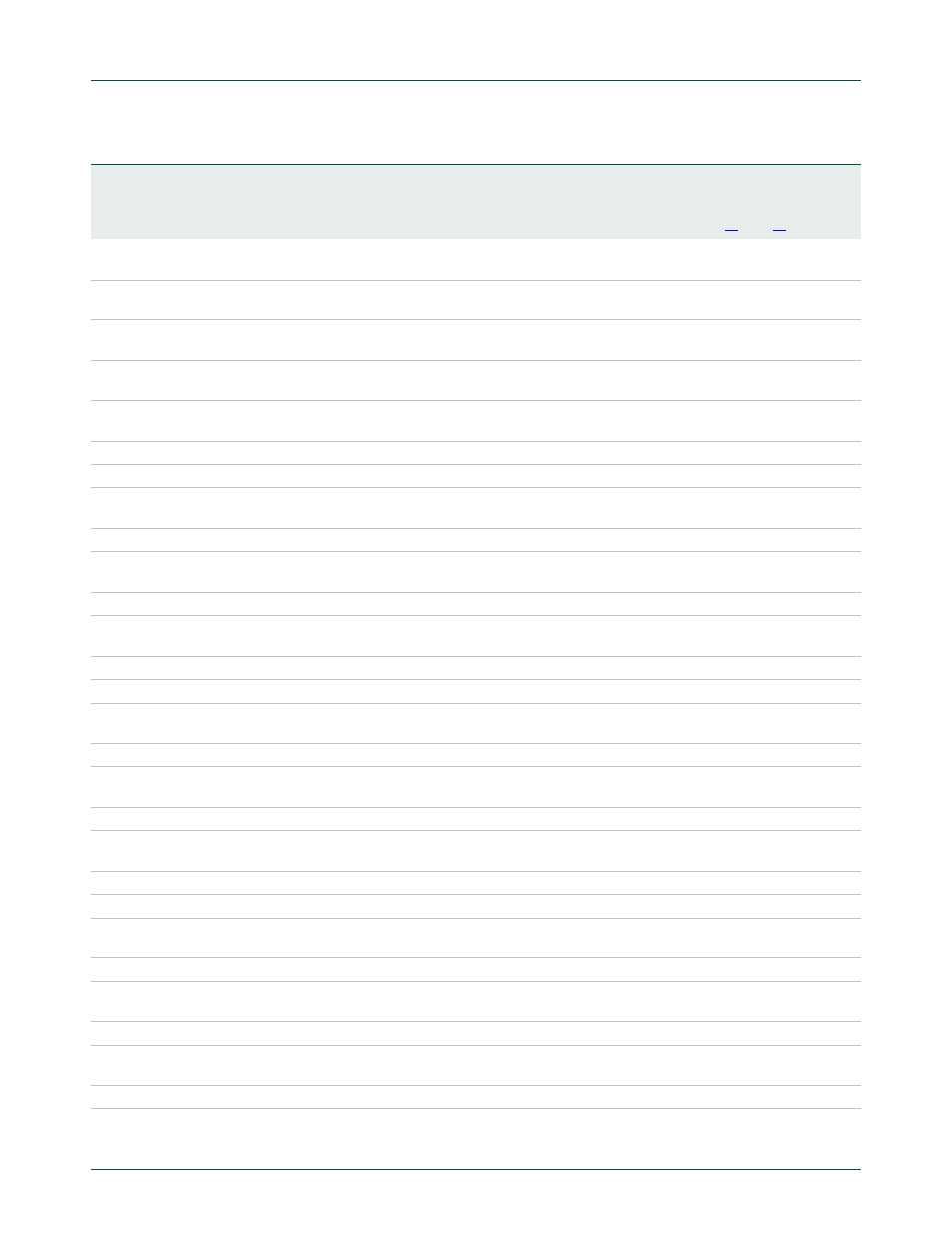

0xFFE0 8124

EMCDynamic RasCas1

Selects the RAS and CAS latencies for dynamic memory

chip select 1.

-

0x303 R/W

0xFFE0 8140

EMCDynamic Config2

Selects the configuration information for dynamic

memory chip select 2.

-

0x0

R/W

0xFFE0 8144

EMCDynamic RasCas2

Selects the RAS and CAS latencies for dynamic memory

chip select 2.

-

0x303 R/W

0xFFE0 8160

EMCDynamic Config3

Selects the configuration information for dynamic

memory chip select 3.

-

0x0

R/W

0xFFE0 8164

EMCDynamic RasCas3

Selects the RAS and CAS latencies for dynamic memory

chip select 3.

-

0x303 R/W

0xFFE0 8200

EMCStatic Config0

Selects the memory configuration for static chip select 0. -

0x0

R/W

0xFFE0 8204

EMCStatic WaitWen0

Selects the delay from chip select 0 to write enable.

-

0x0

R/W

0xFFE0 8208

EMCStatic WaitOen0

Selects the delay from chip select 0 or address change,

whichever is later, to output enable.

-

0x0

R/W

0xFFE0 820C

EMCStatic WaitRd0

Selects the delay from chip select 0 to a read access.

-

0x1F

R/W

0xFFE0 8210

EMCStatic WaitPage0

Selects the delay for asynchronous page mode

sequential accesses for chip select 0.

-

0x1F

R/W

0xFFE0 8214

EMCStatic WaitWr0

Selects the delay from chip select 0 to a write access.

-

0x1F

R/W

0xFFE0 8218

EMCStatic WaitTurn0

Selects the number of bus turnaround cycles for chip

select 0.

-

0xF

R/W

0xFFE0 8220

EMCStatic Config1

Selects the memory configuration for static chip select 1. -

0x0

R/W

0xFFE0 8224

EMCStatic WaitWen1

Selects the delay from chip select 1 to write enable.

-

0x0

R/W

0xFFE0 8228

EMCStatic WaitOen1

Selects the delay from chip select 1 or address change,

whichever is later, to output enable.

-

0x0

R/W

0xFFE0 822C

EMCStatic WaitRd1

Selects the delay from chip select 1 to a read access.

-

0x1F

R/W

0xFFE0 8230

EMCStatic WaitPage1

Selects the delay for asynchronous page mode

sequential accesses for chip select 1.

-

0x1F

R/W

0xFFE0 8234

EMCStatic WaitWr1

Selects the delay from chip select 1 to a write access.

-

0x1F

R/W

0xFFE0 8238

EMCStatic WaitTurn1

Selects the number of bus turnaround cycles for chip

select 1.

-

0xF

R/W

0xFFE0 8240

EMCStatic Config2

Selects the memory configuration for static chip select 2. -

0x0

R/W

0xFFE0 8244

EMCStatic WaitWen2

Selects the delay from chip select 2 to write enable.

-

0x0

R/W

0xFFE0 8248

EMCStatic WaitOen2

Selects the delay from chip select 2 or address change,

whichever is later, to output enable.

-

0x0

R/W

0xFFE0 824C

EMCStatic WaitRd2

Selects the delay from chip select 2 to a read access.

-

0x1F

R/W

0xFFE0 8250

EMCStatic WaitPage2

Selects the delay for asynchronous page mode

sequential accesses for chip select 2.

-

0x1F

R/W

0xFFE0 8254

EMCStatic WaitWr2

Selects the delay from chip select 2 to a write access.

-

0x1F

R/W

0xFFE0 8258

EMCStatic WaitTurn2

Selects the number of bus turnaround cycles for chip

select 2.

-

0xF

R/W

0xFFE0 8260

EMCStatic Config3

Selects the memory configuration for static chip select 3. -

0x0

R/W

0xFFE0 8264

EMCStatic WaitWen3

Selects the delay from chip select 3 to write enable.

-

0x0

R/W

Table 67.

Summary of EMC registers

…continued

Address

Register Name

Description

Warm

Reset

Value

[1]

POR

Reset

Value

[1]

Type