Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 322

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

322 of 792

NXP Semiconductors

UM10237

Chapter 12: LPC24XX LCD controller

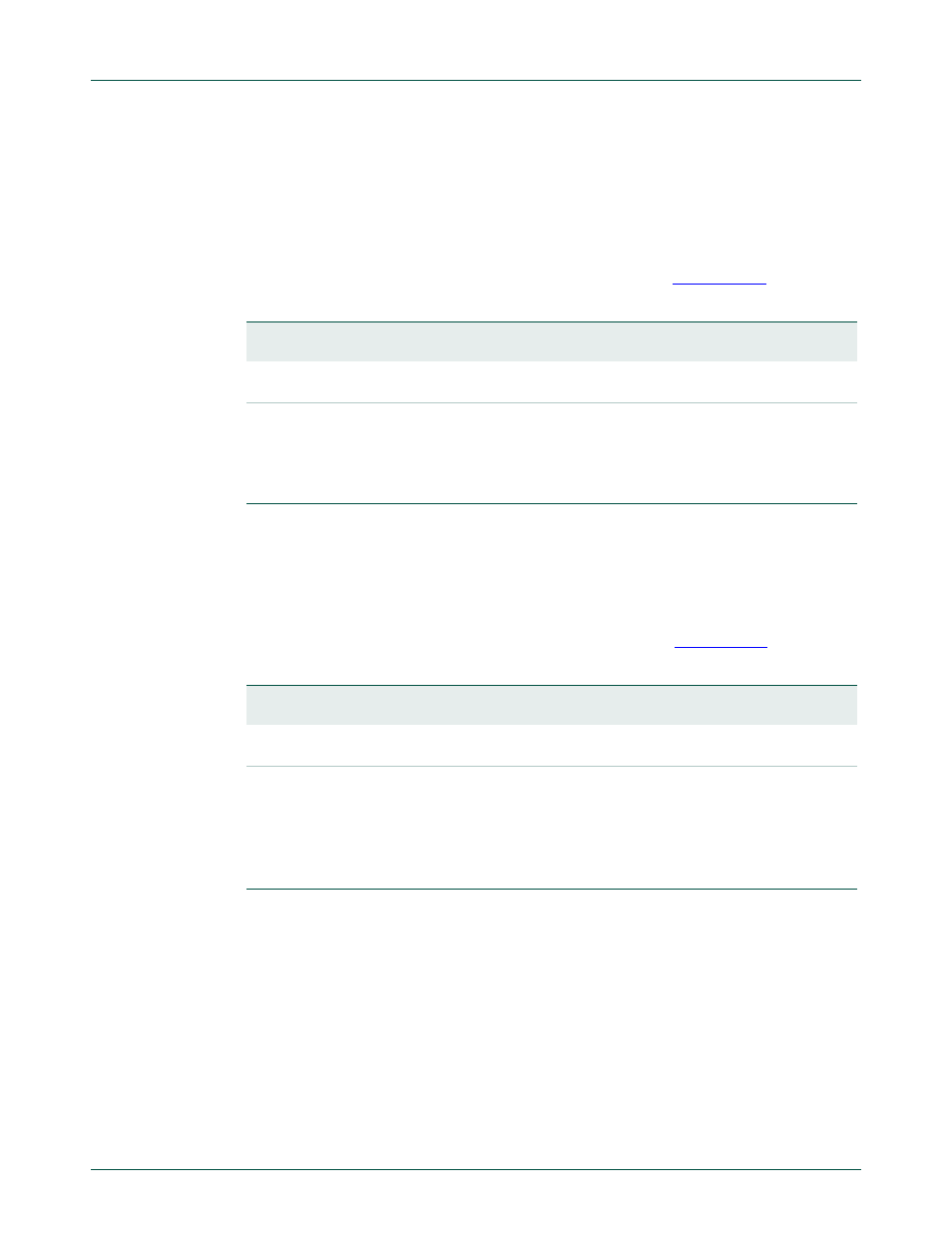

7.25 Cursor Raw Interrupt Status register (CRSR_INTRAW, RW - 0xFFE1

0C28)

The CRSR_INTRAW register is set to indicate a cursor interrupt. When enabled via the

CrsrIM bit in the CRSR_INTMSK register, provides the interrupt to the system interrupt

controller.

The contents of the CRSR_INTRAW register are described in

7.26 Cursor Masked Interrupt Status register (CRSR_INTSTAT, RW -

0xFFE1 0C2C)

The CRSR_INTSTAT register is set to indicate a cursor interrupt providing that the

interrupt is not masked in the

CRSR_INTMSK

register.

The contents of the CRSR_INTSTAT register are described in

.

Table 284. Cursor Raw Interrupt Status register (CRSR_INTRAW, RW - 0xFFE1 0C28)

Bits

Function

Description

Reset

value

31:1

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

0

CrsrRIS

Cursor raw interrupt status.

The cursor interrupt status is set immediately after the last data

is read from the cursor image for the current frame.

This bit is cleared by writing to the CrsrIC bit in the

CRSR_INTCLR register.

0x0

Table 285. Cursor Masked Interrupt Status register (CRSR_INTSTAT, RW - 0xFFE1 0C2C)

Bits

Function

Description

Reset

value

31:1

reserved

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

-

0

CrsrMIS

Cursor masked interrupt status.

The cursor interrupt status is set immediately after the last data

read from the cursor image for the current frame, providing that

the corresponding bit in the CRSR_INTMSK register is set.

The bit remains clear if the CRSR_INTMSK register is clear.

This bit is cleared by writing to the CRSR_INTCLR register.

0x0