9 programming a dma channel, Register description, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 720

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

720 of 792

NXP Semiconductors

UM10237

Chapter 32: LPC24XX General Purpose DMA (GPDMA) controller

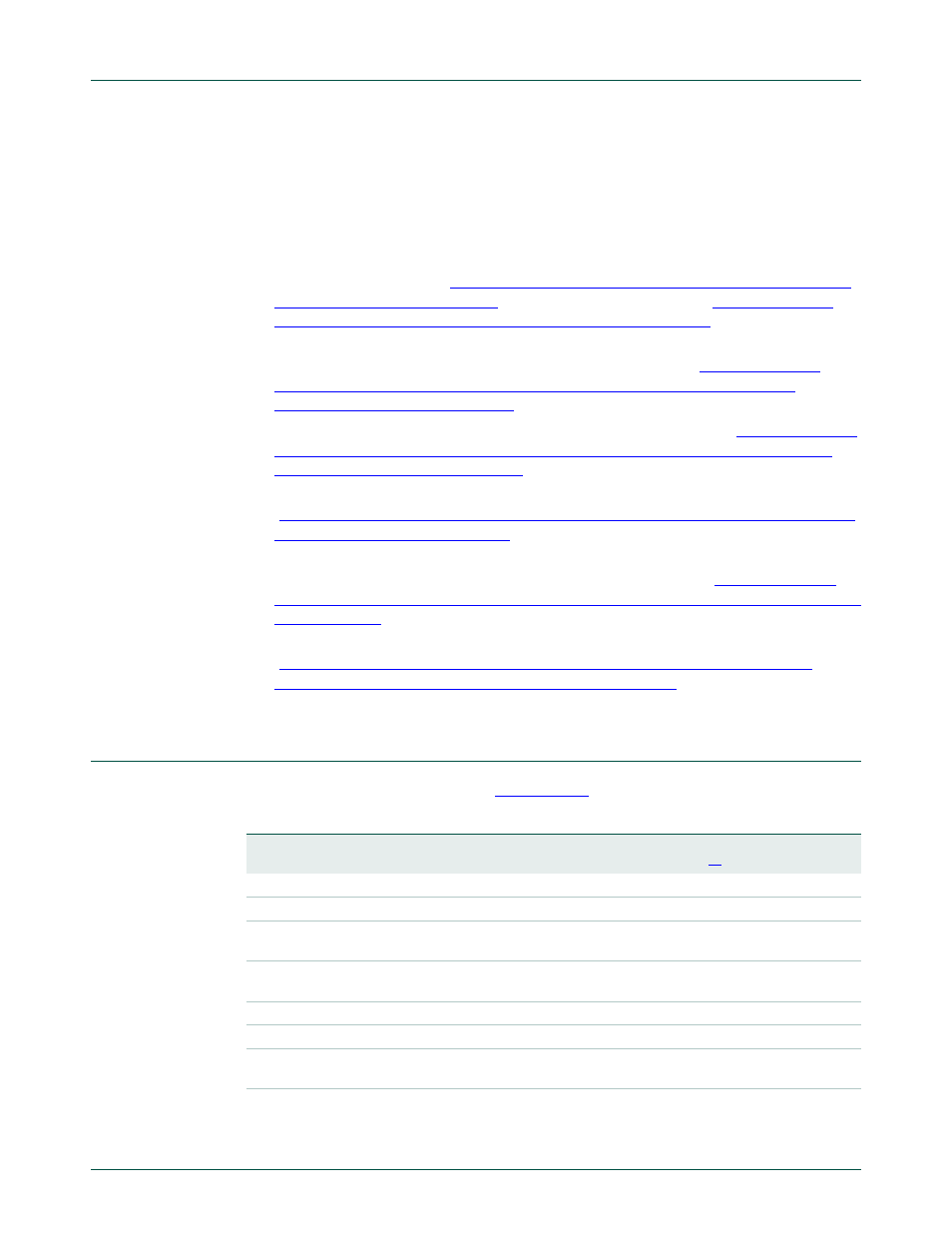

5.9 Programming a DMA channel

To program a DMA channel:

1. Choose a free DMA channel with the priority required. DMA channel 0 has the highest

priority and DMA channel 1 the lowest priority.

2. Clear any pending interrupts on the channel to be used by writing to the

DMACIntTCClr Register (

Section 32–6.1.3 “Interrupt Terminal Count Clear Register

) and DMACIntErrClr Register (

“Interrupt Error Clear Register (DMACIntErrClr - 0xFFE0 4010)”

). The previous

channel operation might have left interrupts active.

3. Write the source address into the DMACCxSrcAddr Register (

“Channel Source Address Registers (DMACC0SrcAddr - 0xFFE0 4100 and

DMACC1SrcAddr - 0xFFE0 4120)”

4. Write the destination address into the DMACCxDestAddr Register (

5. Write the address of the next Linked List Item (LLI) into the DMACCxLLI Register

Section 32–6.2.3 “Channel Linked List Item Registers (DMACC0LLI - 0xFFE0 4108

). If the transfer consists of a single packet of data

then 0 must be written into this register.

6. Write the control information into the DMACCxControl Register (

“Channel Control Registers (DMACC0Control - 0xFFE0 410C and DMACC0Control -

0xFFE0 412C)”

7. Write the channel configuration information into the DMACCxConfiguration Register

Section 32–6.2.6 “Channel Configuration Registers (DMACC0Configuration -

0xFFE0 4110 and DMACC1Configuration - 0xFFE0 4130)”

). If the Enable bit is set

then the DMA channel is automatically enabled.

6.

Register description

The GPDMA registers are shown in

Table 652. Summary of GPDMA registers

Name

Description

Access Reset

Value

Address

General Registers

DMACIntStatus

Interrupt Status Register

RO

0x0

0xFFE0 4000

DMACIntTCStatus

Interrupt Terminal Count

Status Register

RO

0x0

0xFFE0 4004

DMACIntTCClear

Interrupt Terminal Count Clear

Register

WO

-

0xFFE0 4008

DMACIntErrorStatus

Interrupt Error Status Register

RO

0x0

0xFFE0 400C

DMACIntErrClr

Interrupt Error Clear Register

WO

-

0xFFE0 4010

DMACRawIntTCStatus

Raw Interrupt Terminal Count

Status Register

RO

-

0xFFE0 4014

DMACRawIntErrorStatus Raw Error Interrupt Status

Register

RO

-

0xFFE0 4018