3 set mode (command: 0xf3, data: write 1 byte), Table 13–349, Section 13–11.3 – NXP Semiconductors LPC24XX UM10237 User Manual

Page 365: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

365 of 792

NXP Semiconductors

UM10237

Chapter 13: LPC24XX USB device controller

11.3 Set Mode (Command: 0xF3, Data: write 1 byte)

[1]

This bit should be reset to 0 if the DMA is enabled for any of the Interrupt OUT endpoints.

[2]

This bit should be reset to 0 if the DMA is enabled for any of the Bulk OUT endpoints.

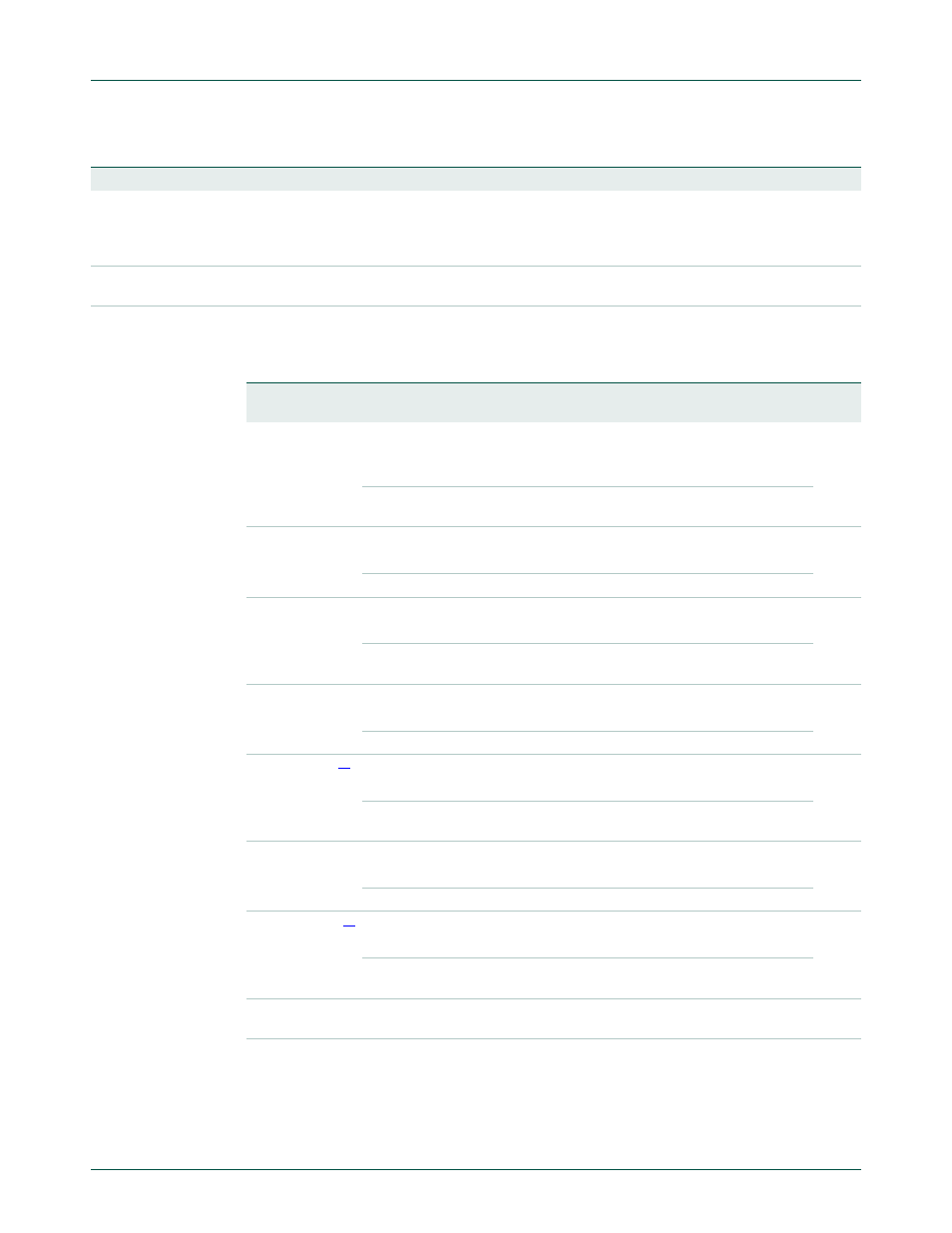

Table 349. Configure Device Register bit description

Bit

Symbol

Description

Reset value

0

CONF_DEVICE

Device is configured. All enabled non-control endpoints will respond. This

bit is cleared by hardware when a bus reset occurs. When set, the

UP_LED signal is driven LOW if the device is not in the suspended state

(SUS=0).

7:1

-

Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

Table 350. Set Mode Register bit description

Bit

Symbol

Value Description

Reset

value

0

AP_CLK

Always PLL Clock.

0

0

USB_NEED_CLK is functional; the 48 MHz clock can be

stopped when the device enters suspend state.

1

USB_NEED_CLK is fixed to 1; the 48 MHz clock cannot be

stopped when the device enters suspend state.

1

INAK_CI

Interrupt on NAK for Control IN endpoint.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed IN transactions generate interrupts.

2

INAK_CO

Interrupt on NAK for Control OUT endpoint.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed OUT transactions generate

interrupts.

3

INAK_II

Interrupt on NAK for Interrupt IN endpoint.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed IN transactions generate interrupts.

4

INAK_IO

Interrupt on NAK for Interrupt OUT endpoints.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed OUT transactions generate

interrupts.

5

INAK_BI

Interrupt on NAK for Bulk IN endpoints.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed IN transactions generate interrupts.

6

Interrupt on NAK for Bulk OUT endpoints.

0

0

Only successful transactions generate an interrupt.

1

Both successful and NAKed OUT transactions generate

interrupts.

7

-

-

Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA