Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 409

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

409 of 792

NXP Semiconductors

UM10237

Chapter 15: LPC24XX USB OTG controller

7.14 I2C Clock High Register (I2C_CLKHI - 0xFFE0 C30C)

The CLK register holds a terminal count for counting 48 MHz clock cycles to create the

high period of the slower I

2

C serial clock, SCL.

3

DRMIE

Master Transmitter Data Request Interrupt Enable. This enables the DRMI interrupt which

signals that the master transmitter has run out of data, has not issued a STOP, and is

holding the SCL line low.

0

0

Disable the DRMI interrupt.

1

Enable the DRMI interrupt.

4

DRSIE

Slave Transmitter Data Request Interrupt Enable. This enables the DRSI interrupt which

signals that the slave transmitter has run out of data and the last byte was acknowledged,

so the SCL line is being held low.

0

0

Disable the DRSI interrupt.

1

Enable the DRSI interrupt.

5

REFIE

Receive FIFO Full Interrupt Enable. This enables the Receive FIFO Full interrupt to

indicate that the receive FIFO cannot accept any more data.

0

0

Disable the RFFI.

1

Enable the RFFI.

6

RFDAIE

Receive Data Available Interrupt Enable. This enables the DAI interrupt to indicate that

data is available in the receive FIFO (i.e. not empty).

0

0

Disable the DAI.

1

Enable the DAI.

7

TFFIE

Transmit FIFO Not Full Interrupt Enable. This enables the Transmit FIFO Not Full interrupt

to indicate that the more data can be written to the transmit FIFO. Note that this is not full.

It is intended help the CPU to write to the I

2

C block only when there is room in the FIFO

and do this without polling the status register.

0

0

Disable the TFFI.

1

Enable the TFFI.

8

SRST

Soft reset. This is only needed in unusual circumstances. If a device issues a start

condition without issuing a stop condition. A system timer may be used to reset the I

2

C if

the bus remains busy longer than the time-out period. On a soft reset, the Tx and Rx

FIFOs are flushed, I2C_STS register is cleared, and all internal state machines are reset

to appear idle. The I2C_CLKHI, I2C_CLKLO and I2C_CTL (except Soft Reset Bit) are

NOT modified by a soft reset.

0

0

See the text.

1

Reset the I

2

C to idle state. Self clearing.

31:9 -

NA

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

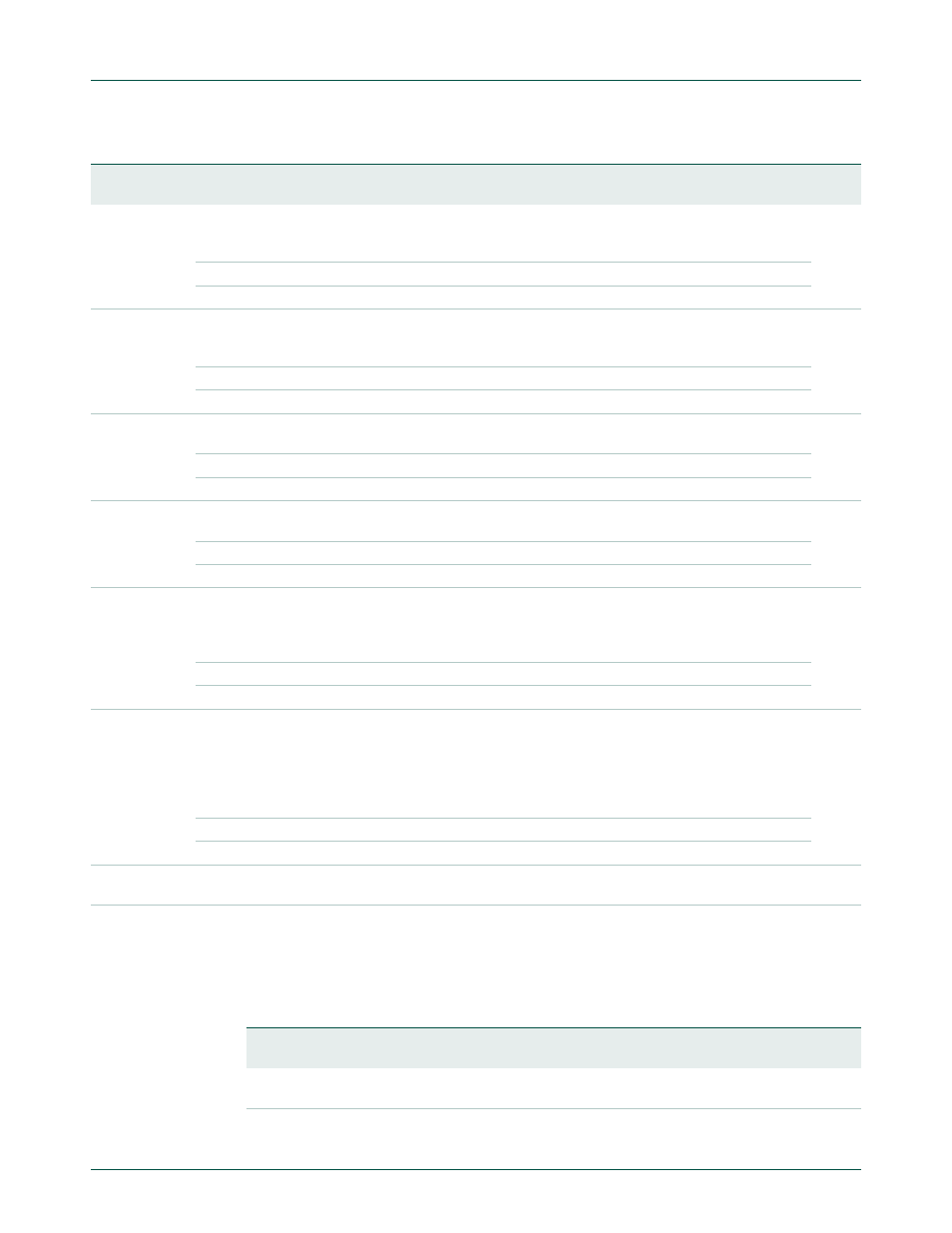

Table 373. I2C Control register (I2C_CTL - address 0xFFE0 C308) bit description

Bit

Symbol

Value

Description

Reset

Value

Table 374. I2C_CLKHI register (I2C_CLKHI - address 0xFFE0 C30C) bit description

Bit

Symbol

Description

Reset

Value

7:0

CDHI

Clock divisor high. This value is the number of 48 MHz

clocks the serial clock (SCL) will be high.

0xB9