Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 340

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

340 of 792

NXP Semiconductors

UM10237

Chapter 13: LPC24XX USB device controller

9.3.2 USB Device Interrupt Status register (USBDevIntSt - 0xFFE0 C200)

The USBDevIntSt register holds the status of each interrupt. A 0 indicates no interrupt and

1 indicates the presence of the interrupt. USBDevIntSt is a read only register.

8

USB_NEED_CLK

USB need clock indicator. This bit is set to 1 when USB activity or a

change of state on the USB data pins is detected, and it indicates that a

PLL supplied clock of 48 MHz is needed. Once USB_NEED_CLK

becomes one, it it resets to zero 5 ms after the last packet has been

received/sent, or 2 ms after the Suspend Change (SUS_CH) interrupt

has occurred. A change of this bit from 0 to 1 can wake up the

microcontroller if activity on the USB bus is selected to wake up the part

from the Power-down mode (see

Section 4–3.4.8 “Interrupt Wakeup

Register (INTWAKE - 0xE01F C144)”

for details). Also see

4–3.2.10 “PLL and Power-down mode”

and

Control for Peripherals register (PCONP - 0xE01F C0C4)”

for

considerations about the PLL and invoking the Power-down mode. This

bit is read only.

0

30:9

-

Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

31

EN_USB_INTS

Enable all USB interrupts. When this bit is cleared, the Vectored

Interrupt Controller does not see the ORed output of the USB interrupt

lines.

1

Table 297. USB Interrupt Status register (USBIntSt - address 0xE01F C1C0) bit description

Bit

Symbol

Description

Reset

value

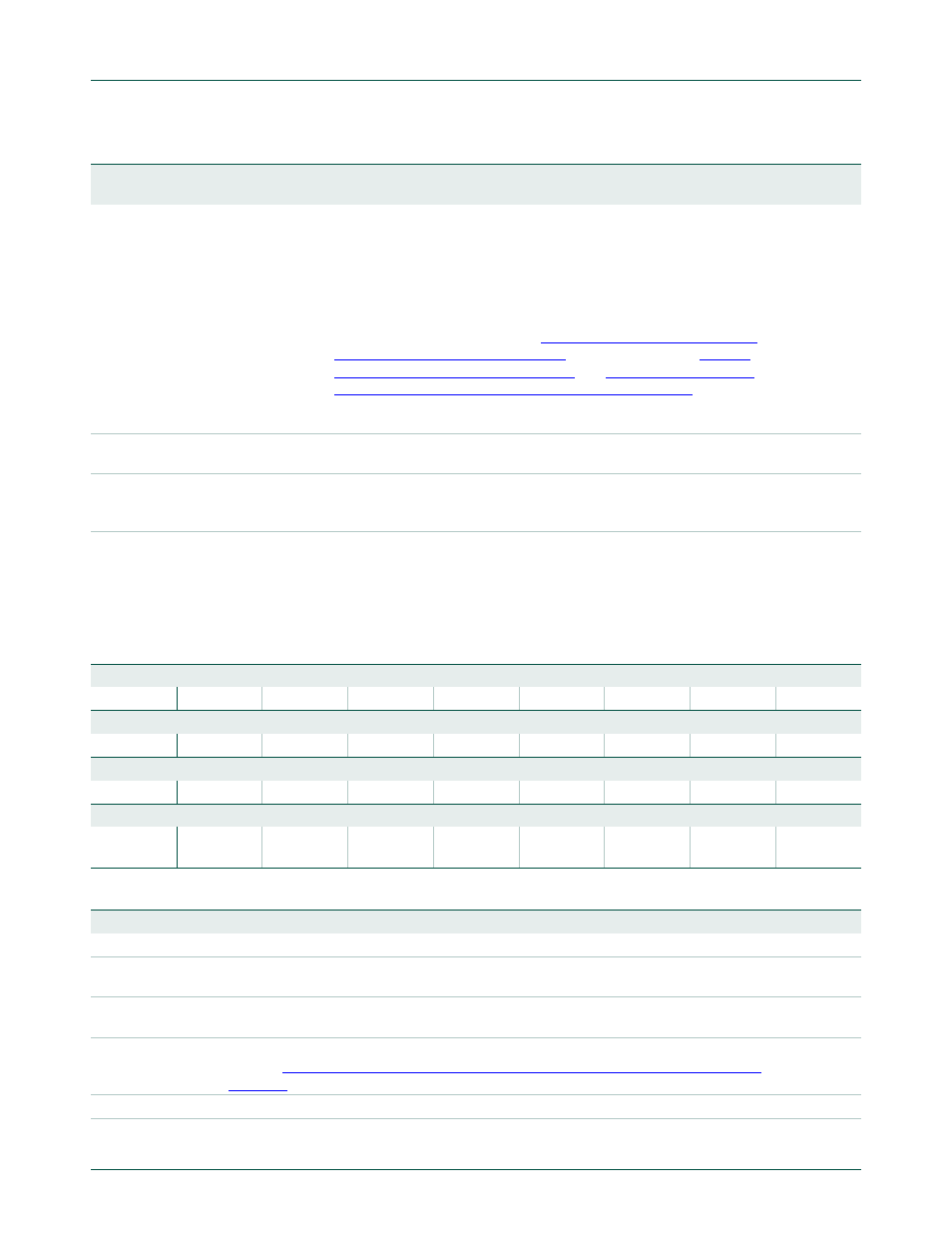

Table 298. USB Device Interrupt Status register (USBDevIntSt - address 0xFFE0 C200) bit allocation

Reset value: 0x0000 0000

Bit

31

30

29

28

27

26

25

24

Symbol

-

-

-

-

-

-

-

-

Bit

23

22

21

20

19

18

17

16

Symbol

-

-

-

-

-

-

-

-

Bit

15

14

13

12

11

10

9

8

Symbol

-

-

-

-

-

-

ERR_INT

EP_RLZED

Bit

7

6

5

4

3

2

1

0

Symbol

TxENDPKT

Rx

ENDPKT

CDFULL

CCEMPTY

DEV_STAT

EP_SLOW

EP_FAST

FRAME

Table 299. USB Device Interrupt Status register (USBDevIntSt - address 0xFFE0 C200) bit description

Bit

Symbol

Description

Reset value

0

FRAME

The frame interrupt occurs every 1 ms. This is used in isochronous packet transfers.

0

1

EP_FAST

Fast endpoint interrupt. If an Endpoint Interrupt Priority register (USBEpIntPri) bit is

set, the corresponding endpoint interrupt will be routed to this bit.

0

2

EP_SLOW

Slow endpoints interrupt. If an Endpoint Interrupt Priority Register (USBEpIntPri) bit is

not set, the corresponding endpoint interrupt will be routed to this bit.

0

3

DEV_STAT

Set when USB Bus reset, USB suspend change or Connect change event occurs.

Refer to

Section 13–11.6 “Set Device Status (Command: 0xFE, Data: write 1 byte)” on

0

4

CCEMPTY

The command code register (USBCmdCode) is empty (New command can be written). 1

5

CDFULL

Command data register (USBCmdData) is full (Data can be read now).

0