1 ethernet mac register definitions, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 220

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

220 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

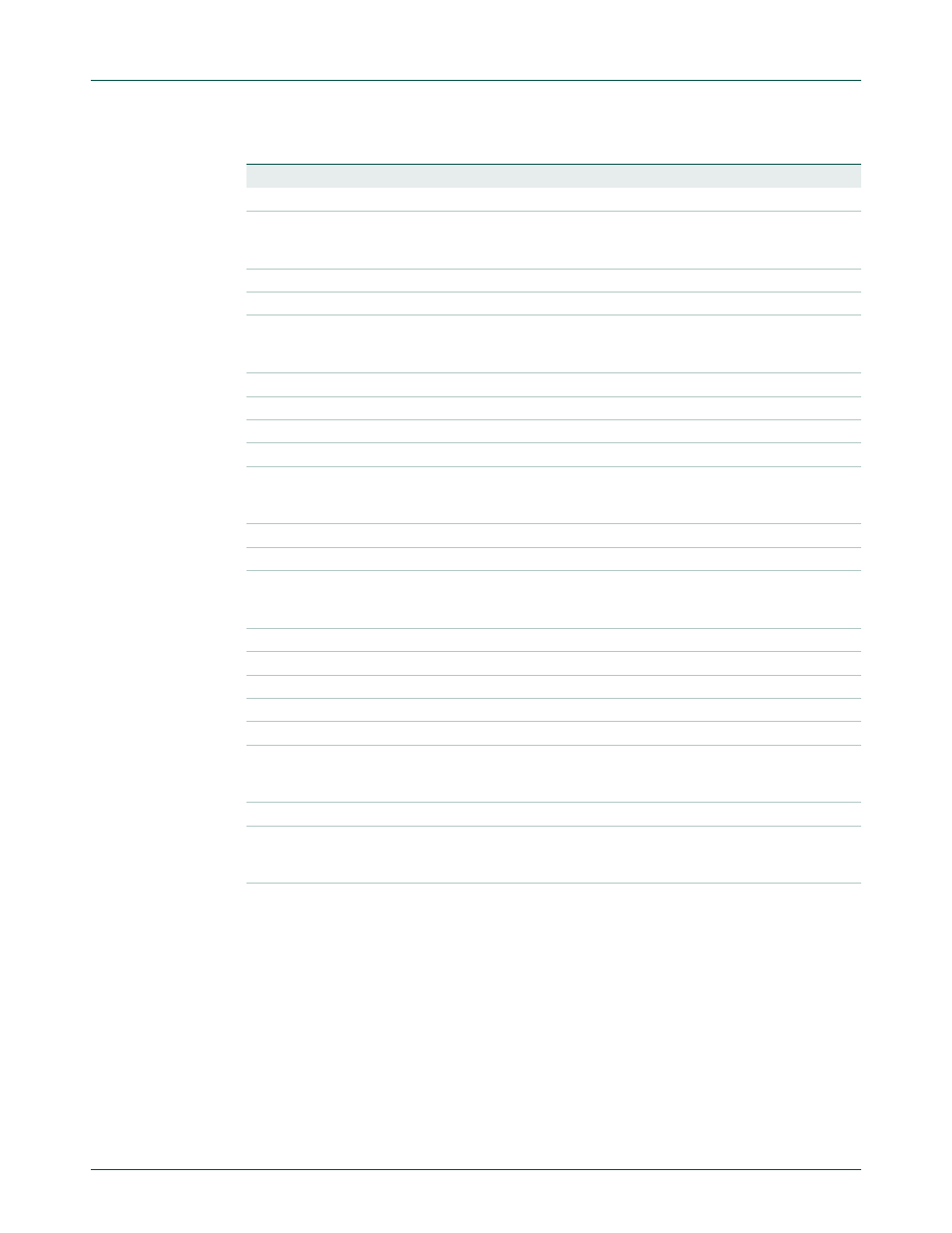

The third column in the table lists the accessibility of the register: read-only, write-only,

read/write.

All AHB register write transactions except for accesses to the interrupt registers are

posted i.e. the AHB transaction will complete before write data is actually committed to the

register. Accesses to the interrupt registers will only be completed by accepting the write

data when the data has been committed to the register.

7.1 Ethernet MAC register definitions

This section defines the bits in the individual registers of the Ethernet block register map.

RSV

0xFFE0 0160

RO

Receive status vector register.

-

0xFFE0 0164 to

0xFFE0 016C

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

FlowControlCounter

0xFFE0 0170

R/W Flow control counter register.

FlowControlStatus

0xFFE0 0174

RO

Flow control status register.

-

0xFFE0 0178 to

0xFFE0 01FC

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

Rx filter registers

RxFliterCtrl

0xFFE0 0200

Receive filter control register.

RxFilterWoLStatus

0xFFE0 0204

Receive filter WoL status register.

RxFilterWoLClear

0xFFE0 0208

Receive filter WoL clear register.

-

0xFFE0 020C

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

HashFilterL

0xFFE0 0210

Hash filter table LSBs register.

HashFilterH

0xFFE0 0214

Hash filter table MSBs register.

-

0xFFE0 0218 to

0xFFE0 0FDC

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

Module control registers

IntStatus

0xFFE0 0FE0

RO

Interrupt status register.

IntEnable

0xFFE0 0FE4

R/W Interrupt enable register.

IntClear

0xFFE0 0FE8

WO

Interrupt clear register.

IntSet

0xFFE0 0FEC

WO

Interrupt set register.

-

0xFFE0 0FF0

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

PowerDown

0xFFE0 0FF4

R/W Power-down register.

-

0xFFE0 0FF8

-

Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit

is not defined.

Table 186. Summary of Ethernet registers

Symbol

Address

R/W Description