11 status flags, 12 crc generator, 13 data fifo – NXP Semiconductors LPC24XX UM10237 User Manual

Page 561: Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

561 of 792

NXP Semiconductors

UM10237

Chapter 21: LPC24XX SD/MMC card interface

5.3.11 Status flags

lists the data path status flags (see

Section 21–6.11 “Status Register

(MCIStatus - 0xE008 C034)” on page 569

for more information).

5.3.12 CRC generator

The CRC generator calculates the CRC checksum only for the data bits in a single block,

and is bypassed in data stream mode. The checksum is a 16 bit value:

CRC[15:0] = Remainder [(M(x)

× x

15

) / G(x)]

G(x) = x

16

+ x

12

+ x

5

+ 1

M(x) - (first data bit)

× x

n

+ ... + (last data bit) ¥ X

0

5.3.13 Data FIFO

The data FIFO (first-in-first-out) subunit is a data buffer with transmit and receive logic.

The FIFO contains a 32 bit wide, 16-word deep data buffer, and transmit and receive

logic. Because the data FIFO operates in the APB clock domain (PCLK), all signals from

the subunits in the MCI clock domain (MCLK) are resynchronized.

Depending on TxActive and RxActive, the FIFO can be disabled, transmit enabled, or

receive enabled. TxActive and RxActive are driven by the data path subunit and are

mutually exclusive:

•

The transmit FIFO refers to the transmit logic and data buffer when TxActive is

asserted (see

Section 21–5.3.14 “Transmit FIFO”

)

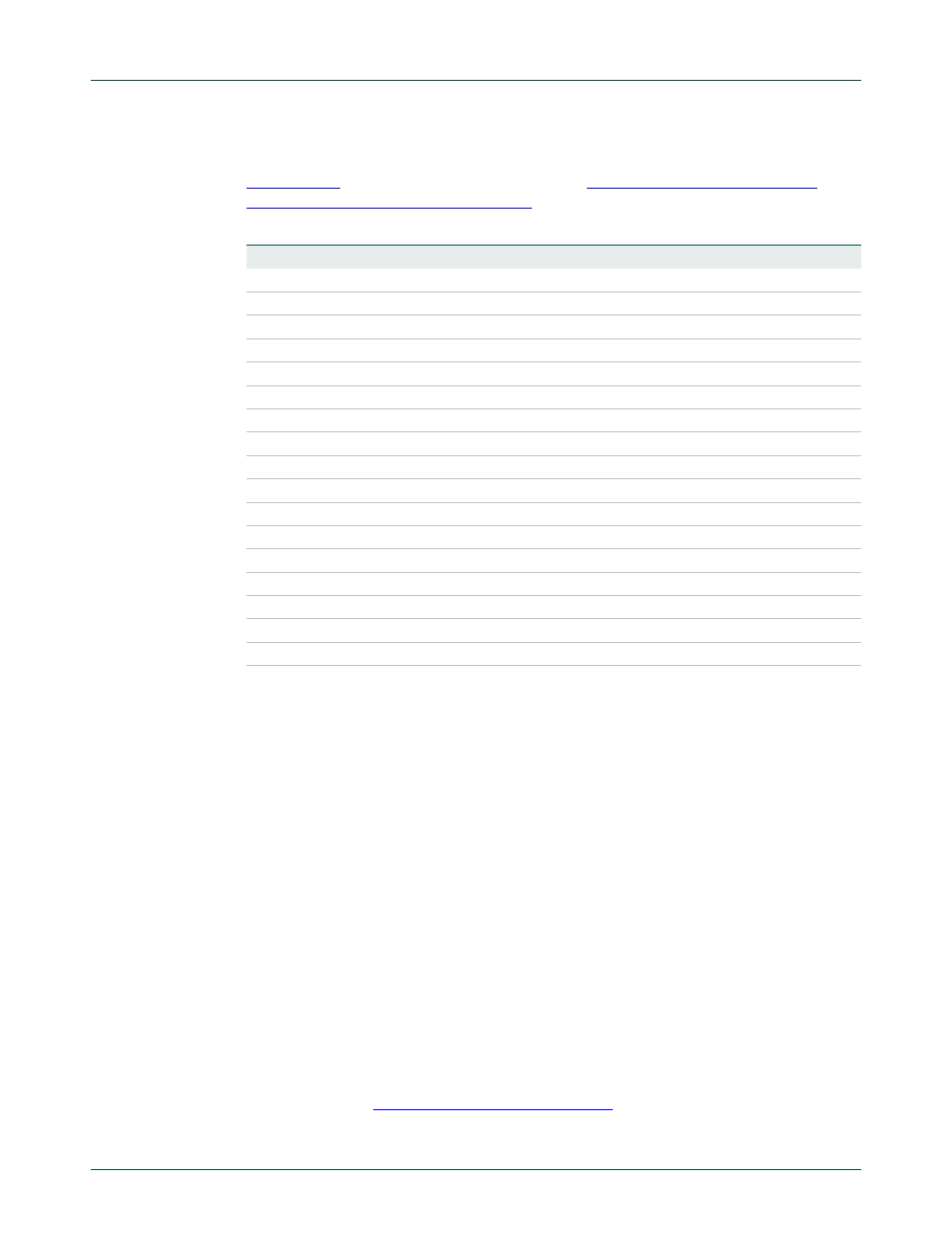

Table 487. Data path status flags

Flag

Description

TxFifoFull

Transmit FIFO is full.

TxFifoEmpty

Transmit FIFO is empty.

TxFifoHalfEmpty

Transmit FIFO is half full.

TxDataAvlbl

Transmit FIFO data available.

TxUnderrun

Transmit FIFO underrun error.

RxFifoFull

Receive FIFO is full.

RxFifoEmpty

Receive FIFO is empty.

RxFifoHalfFull

Receive FIFO is half full.

RxDataAvlbl

Receive FIFO data available.

RxOverrun

Receive FIFO overrun error.

DataBlockEnd

Data block sent/received.

StartBitErr

Start bit not detected on all data signals in wide bus mode.

DataCrcFail

Data packet CRC failed.

DataEnd

Data end (data counter is zero).

DataTimeOut

Data timeout.

TxActive

Data transmission in progress.

RxActive

Data reception in progress.