Table 9–136, Table 9–137, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 185

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

185 of 792

NXP Semiconductors

UM10237

Chapter 9: LPC24XX Pin connect

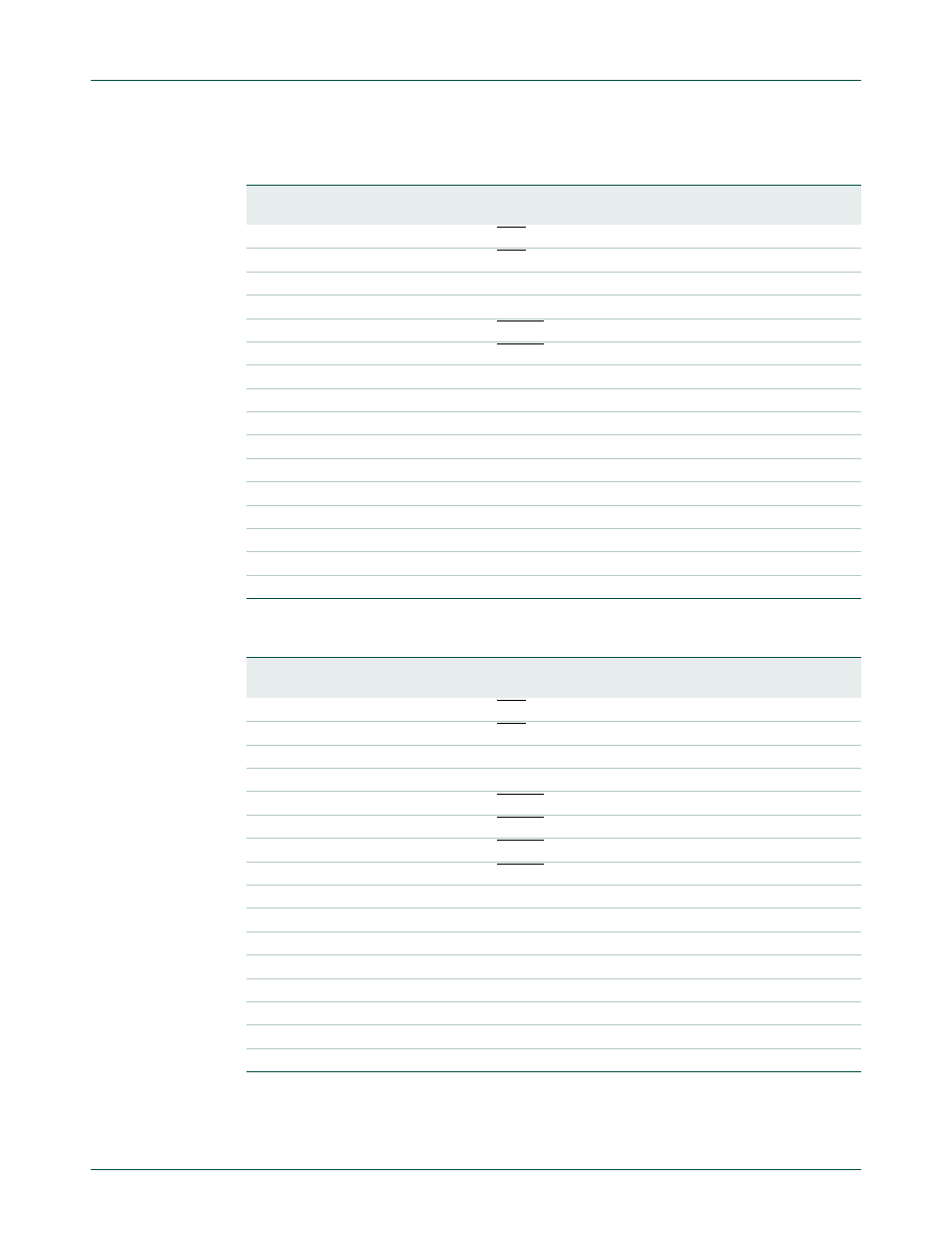

Table 136. LPC2458 pin function select register 5 (PINSEL5 - address 0xE002 C014) bit

description

PINSEL5 Pin

name

Function when

00

Function

when 01

Function

when 10

Function

when 11

Reset

value

1:0

P2[16]

GPIO Port 2.16

CAS

Reserved

Reserved

00

3:2

P2[17]

GPIO Port 2.17

RAS

Reserved

Reserved

00

5:4

P2[18]

GPIO Port 2.18

CLKOUT0

Reserved

Reserved

00

7:6

P2[19]

GPIO Port 2.19

CLKOUT1

Reserved

Reserved

00

9:8

P2[20]

GPIO Port 2.20

DYCS0

Reserved

Reserved

00

11:10

P2[21]

GPIO Port 2.21

DYCS1

Reserved

Reserved

00

13:12

P2[22]

Reserved

Reserved

Reserved

Reserved

00

15:14

P2[23]

Reserved

Reserved

Reserved

Reserved

00

17:16

P2[24]

GPIO Port 2.24

CKEOUT0

Reserved

Reserved

00

19:18

P2[25]

GPIO Port 2.25

CKEOUT1

Reserved

Reserved

00

21:20

P2[26]

Reserved

Reserved

Reserved

Reserved

00

23:22

P2[27]

Reserved

Reserved

Reserved

Reserved

00

25:24

P2[28]

GPIO Port 2.28

DQMOUT0

Reserved

Reserved

00

27:26

P2[29]

GPIO Port 2.29

DQMOUT1

Reserved

Reserved

00

29:28

P2[30]

Reserved

Reserved

Reserved

Reserved

00

31:30

P2[31]

Reserved

Reserved

Reserved

Reserved

00

Table 137. LPC2420/60/68/70/78 pin function select register 5 (PINSEL5 - address

0xE002 C014) bit description

PINSEL5 Pin

name

Function when

00

Function

when 01

Function

when 10

Function

when 11

Reset

value

1:0

P2[16]

GPIO Port 2.16

CAS

Reserved

Reserved

00

3:2

P2[17]

GPIO Port 2.17

RAS

Reserved

Reserved

00

5:4

P2[18]

GPIO Port 2.18

CLKOUT0

Reserved

Reserved

00

7:6

P2[19]

GPIO Port 2.19

CLKOUT1

Reserved

Reserved

00

9:8

P2[20]

GPIO Port 2.20

DYCS0

Reserved

Reserved

00

11:10

P2[21]

GPIO Port 2.21

DYCS1

Reserved

Reserved

00

13:12

P2[22]

GPIO Port 2.22

DYSC2

CAP3[0]

SCK0

00

15:14

P2[23]

GPIO Port 2.23

DYSC3

CAP3[1]

SSEL0

00

17:16

P2[24]

GPIO Port 2.24

CKEOUT0

Reserved

Reserved

00

19:18

P2[25]

GPIO Port 2.25

CKEOUT1

Reserved

Reserved

00

21:20

P2[26]

GPIO Port 2.26

CKEOUT2

MAT3[0]

MISO0

00

23:22

P2[27]

GPIO Port 2.27

CKEOUT3

MAT3[1]

MOSI0

00

25:24

P2[28]

GPIO Port 2.28

DQMOUT0

Reserved

Reserved

00

27:26

P2[29]

GPIO Port 2.29

DQMOUT1

Reserved

Reserved

00

29:28

P2[30]

GPIO Port 2.30

DQMOUT2

MAT3[2]

SDA2

00

31:30

P2[31]

GPIO Port 2.31

DQMOUT3

MAT3[3]

SCL2

00