Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 136

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

136 of 792

NXP Semiconductors

UM10237

Chapter 8: LPC24XX Pin configuration

[1]

5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis.

[2]

5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as a ADC input,

digital section of the pad is disabled.

[3]

5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output,

digital section of the pad is disabled.

[4]

Open-drain 5 V tolerant digital I/O pad, compatible with I

2

C-bus 400 kHz specification. It requires an external pull-up to provide output

functionality. When power is switched off, this pin connected to the I

2

C-bus is floating and does not disturb the I

2

C lines. Open-drain

configuration applies to all functions on this pin.

[5]

Pad provides digital I/O and USB functions. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and

Low-speed mode only).

[6]

5 V tolerant pad with 5 ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

[7]

5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

[8]

Pad provides special analog functionality.

[9]

Pad provides special analog functionality.

[10] Pad provides special analog functionality.

[11] Pad provides special analog functionality.

[12] Pad provides special analog functionality.

[13] Pad provides special analog functionality.

[14] Pad provides special analog functionality.

V

SSIO

H4, P4,

L9, L13,

G13,

D13,

C11,

B4

I

ground: 0 V reference for the digital IO pins.

V

SSCORE

H3, L8,

A10

I

ground: 0 V reference for the core.

V

SSA

F3

I

analog ground: 0 V reference. This should nominally be the same voltage as

V

SSIO

/V

SSCORE

, but should be isolated to minimize noise and error.

V

DD(3V3)

E2, L4,

K8, L11,

J14, E12,

E10,

C5

I

3.3 V supply voltage: This is the power supply voltage for the I/O ports.

n.c.

H1, L12,

G10

I

not connected pins: These pins must be left unconnected (floating).

V

DD(DCDC)(3V3)

G1, N9,

E9

I

3.3 V DC-to-DC converter supply voltage: This is the power supply for the

on-chip DC-to-DC converter.

V

DDA

F2

I

analog 3.3 V pad supply voltage: This should be nominally the same voltage as

V

DD(3V3)

but should be isolated to minimize noise and error. This voltage is used

to power the ADC and DAC.

VREF

I

ADC reference: This should be nominally the same voltage as V

DD(3V3)

but

should be isolated to minimize noise and error. The level on this pin is used as a

reference for ADC and DAC.

VBAT

K1

I

RTC power supply: 3.3 V on this pin supplies the power to the RTC peripheral.

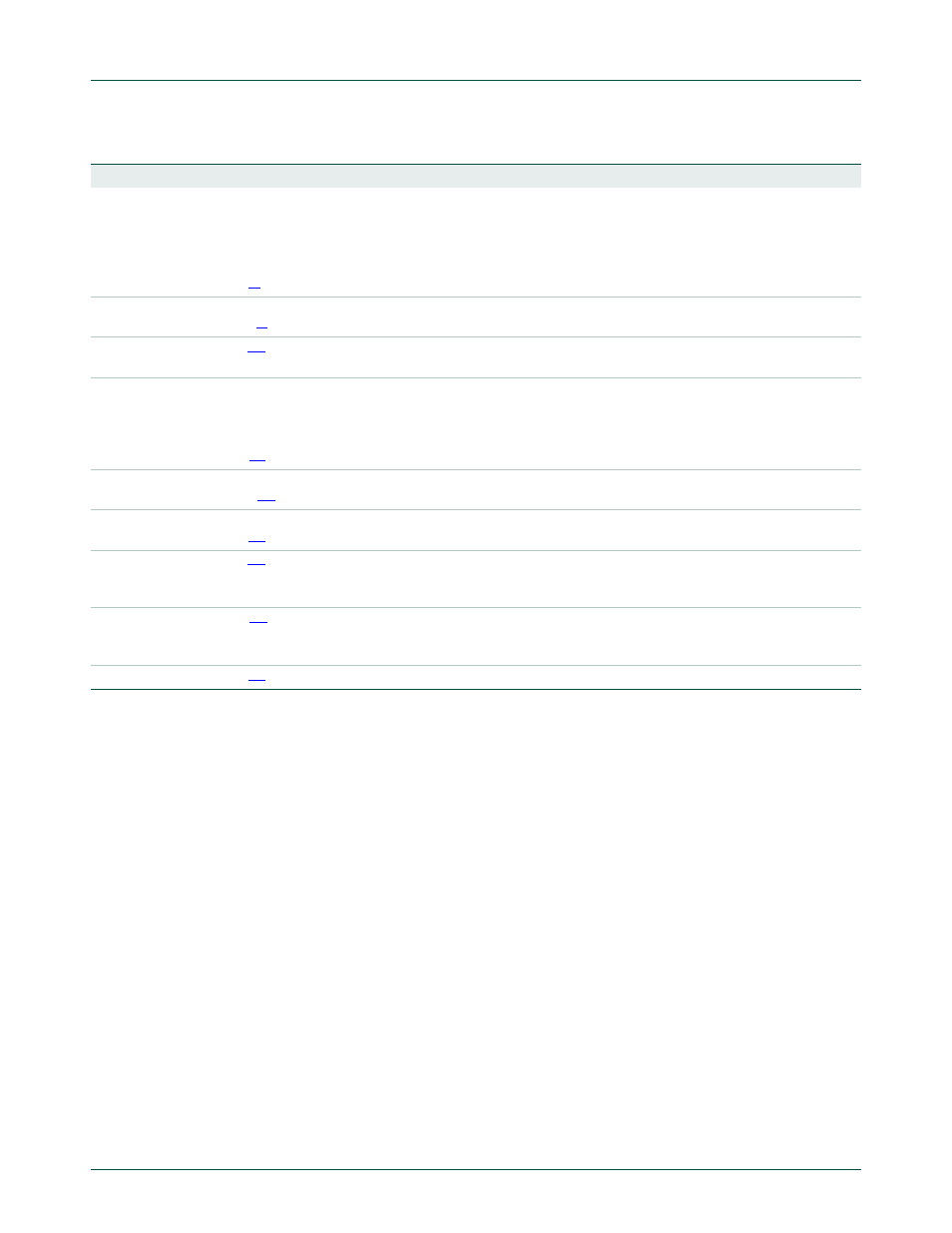

Table 120. Pin description

…continued

Symbol

Ball

Type

Description