Features, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 212

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

212 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

4.

Features

•

Ethernet standards support:

– Supports 10 or 100 Mbps PHY devices including 10 Base-T, 100 Base-TX,

100 Base-FX, and 100 Base-T4.

– Fully compliant with IEEE standard 802.3.

– Fully compliant with 802.3x Full Duplex Flow Control and Half Duplex back

pressure.

– Flexible transmit and receive frame options.

– VLAN frame support.

•

Memory management:

– Independent transmit and receive buffers memory mapped to shared SRAM.

– DMA managers with scatter/gather DMA and arrays of frame descriptors.

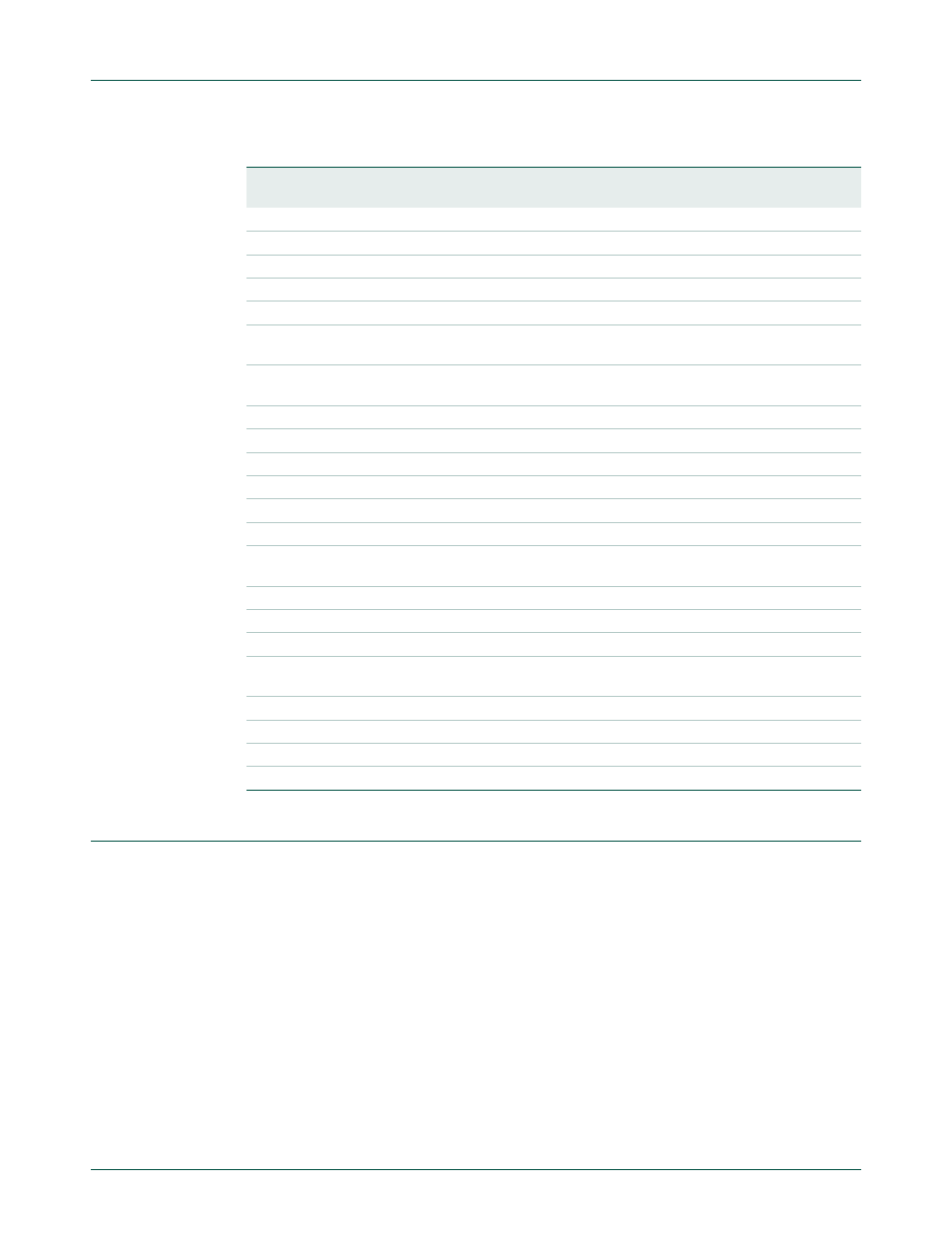

Table 181. Ethernet acronyms, abbreviations, and definitions

Acronym or

Abbreviation

Definition

AHB

Advanced High-performance bus

CRC

Cyclic Redundancy Check

DMA

Direct Memory Access

Double-word

64 bit entity

FCS

Frame Check Sequence (CRC)

Fragment

A (part of an) Ethernet frame; one or multiple fragments can add up to a single

Ethernet frame.

Frame

An Ethernet frame consists of destination address, source address, length

type field, payload and frame check sequence.

Half-word

16 bit entity

LAN

Local Area Network

MAC

Media Access Control sublayer

MII

Media Independent Interface

MIIM

MII management

Octet

An 8 bit data entity, used in lieu of "byte" by IEEE 802.3

Packet

A frame that is transported across Ethernet; a packet consists of a preamble,

a start of frame delimiter and an Ethernet frame.

PHY

Ethernet Physical Layer

RMII

Reduced MII

Rx

Receive

TCP/IP

Transmission Control Protocol / Internet Protocol. The most common

high-level protocol used with Ethernet.

Tx

Transmit

VLAN

Virtual LAN

WoL

Wake-up on LAN

Word

32 bit entity