1 ahb interfaces, Nxp semiconductors, 1 amba ahb slave interface – NXP Semiconductors LPC24XX UM10237 User Manual

Page 287

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

287 of 792

NXP Semiconductors

UM10237

Chapter 12: LPC24XX LCD controller

•

Bus error.

There is also a single combined interrupt that is asserted when any of the individual

interrupts become active.

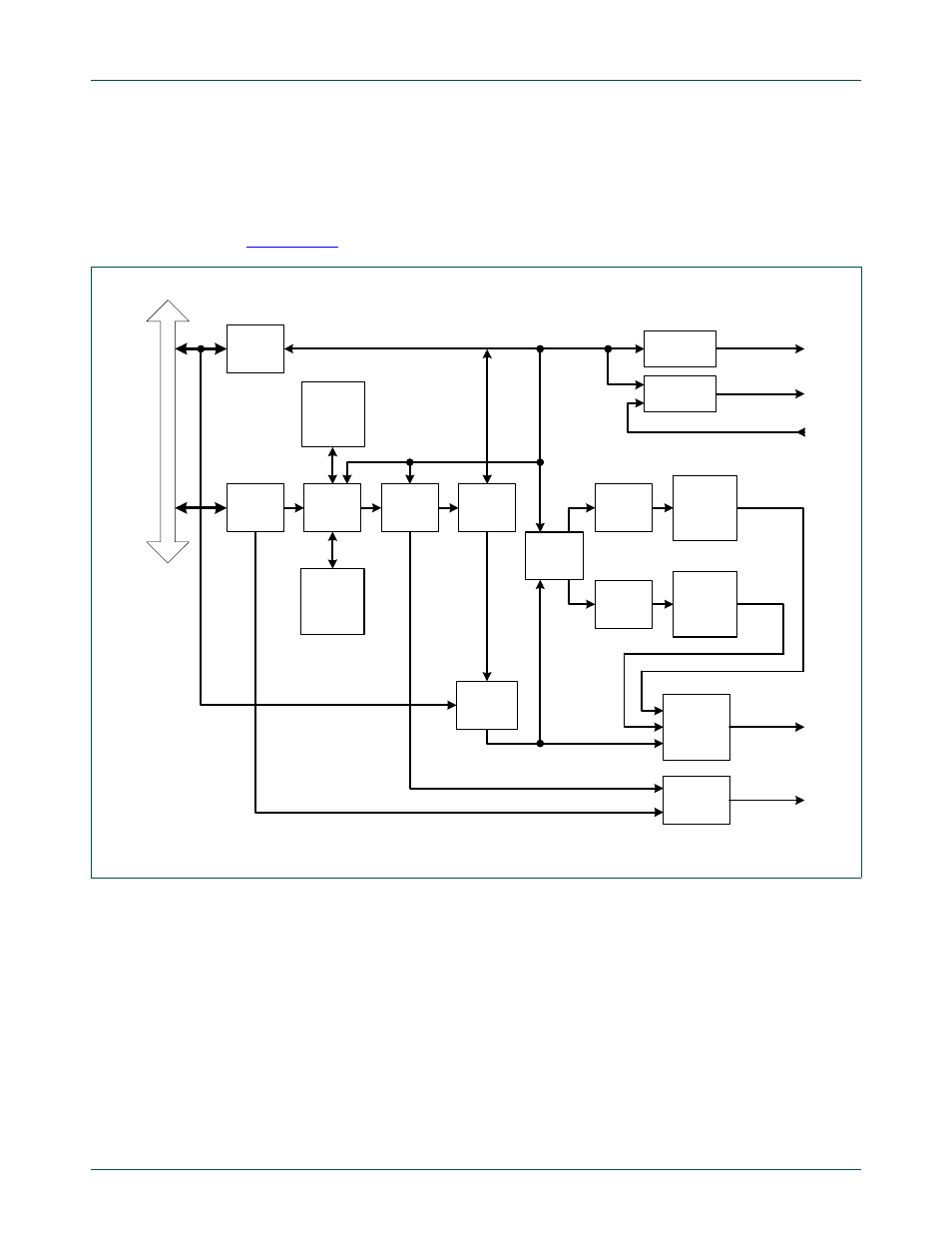

shows a simplified block diagram of the LCD controller.

6.1 AHB interfaces

The LCD controller includes two separate AHB interfaces. The first, an AHB slave

interface, is used primarily by the CPU to access control and data registers within the LCD

controller. The second, an AHB master interface, is used by the LCD controller for DMA

access to display data stored in memory elsewhere in the system. The LCD DMA

controller can only access the 10 kB SRAM on AHB1 and the external memory.

6.1.1 AMBA AHB slave interface

The AHB slave interface connects the LCD controller to the AHB bus and provides CPU

accesses to the registers and palette RAM.

Fig 36. LCD controller block diagram

AHB

slave

interface

AHB

master

interface

A

H

B Bu

s

Panel clock

generator

Timing

controller

LCD panel

clock

LCD control

signals

Upper

panel

DMA

FIFO

Pixel

serializer

Lower

panel

formatter

RAM

palette

(128x32)

Input

FIFO

control

Lower

panel

DMA

FIFO

Upper

panel

output

FIFO

Lower

panel

output

FIFO

Upper

panel

formatter

Upper

STN

Lower

STN

Hardware

Cursor

Gray

scaler

STN/TFT

data

select

LCD panel

data

Interrupt

generation

Interrupt

FIFO underflow

AHB error

LCDCLKIN