Table 11–198, Nxp semiconductors – NXP Semiconductors LPC24XX UM10237 User Manual

Page 226

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

226 of 792

NXP Semiconductors

UM10237

Chapter 11: LPC24XX Ethernet

7.1.11 MII Mgmt Address Register (MADR - 0xFFE0 0028)

The MII Mgmt Address register (MADR) has an address of 0xFFE0 0028. The bit

definition of this register is shown in

7.1.12 MII Mgmt Write Data Register (MWTD - 0xFFE0 002C)

The MII Mgmt Write Data register (MWTD) is a Write Only register with an address of

0xFFE0 002C. The bit definition of this register is shown in

.

7.1.13 MII Mgmt Read Data Register (MRDD - 0xFFE0 0030)

The MII Mgmt Read Data register (MRDD) is a Read Only register with an address of

0xFFE0 0030. The bit definition of this register is shown in

7.1.14 MII Mgmt Indicators Register (MIND - 0xFFE0 0034)

The MII Mgmt Indicators register (MIND) is a Read Only register with an address of

0xFFE0 0034. The bit definition of this register is shown in

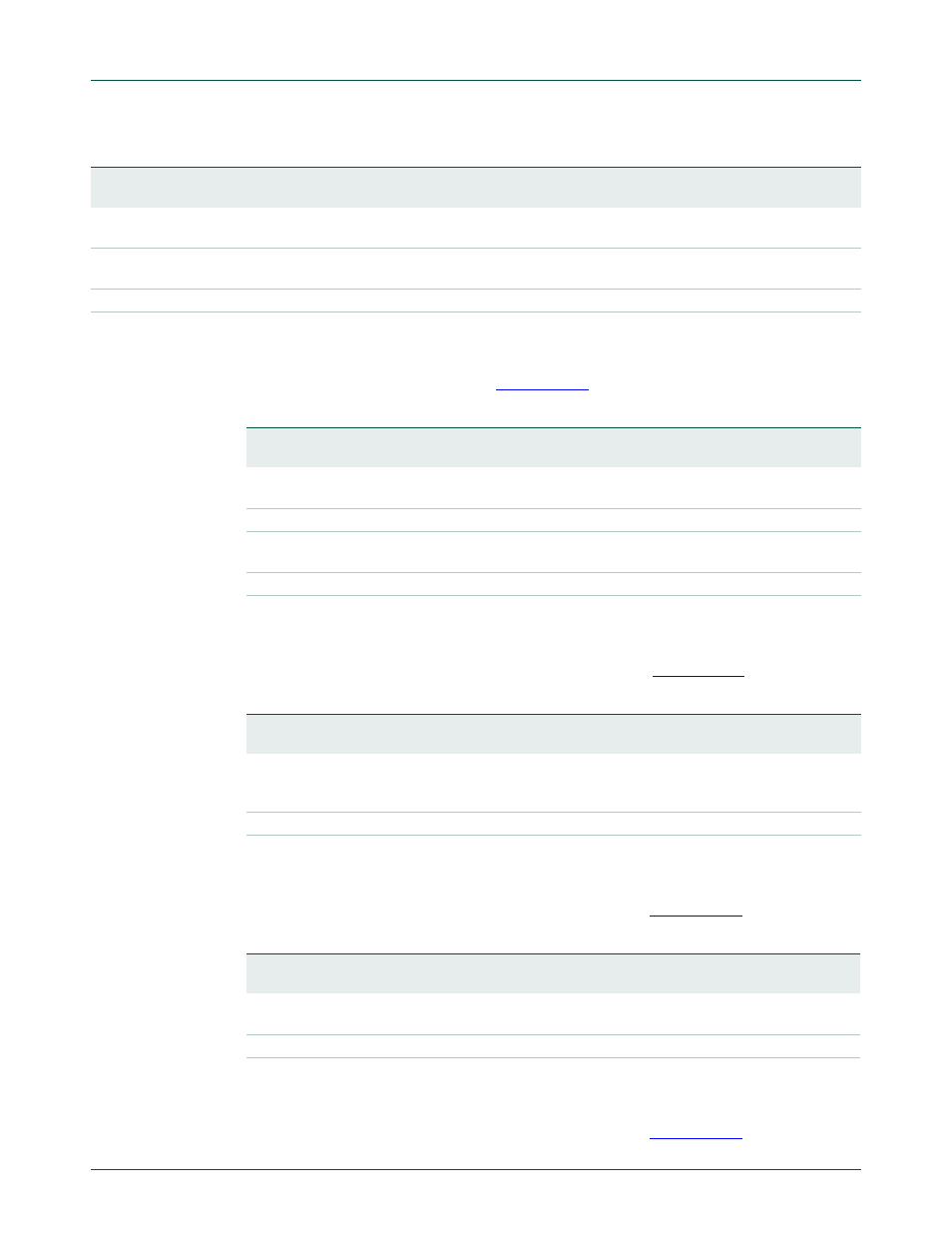

Table 198. MII Mgmt Command register (MCMD - address 0xFFE0 0024) bit description

Bit

Symbol

Function

Reset

value

0

READ

This bit causes the MII Management hardware to perform a single Read cycle. The Read data is

returned in Register MRDD (MII Mgmt Read Data).

0

1

SCAN

This bit causes the MII Management hardware to perform Read cycles continuously. This is

useful for monitoring Link Fail for example.

0

31:2

-

Unused

0x0

Table 199. MII Mgmt Address register (MADR - address 0xFFE0 0028) bit description

Bit

Symbol

Function

Reset

value

4:0

REGISTER

ADDRESS

This field represents the 5 bit Register Address field of Mgmt

cycles. Up to 32 registers can be accessed.

0x0

7:5

-

Unused

0x0

12:8

PHY ADDRESS

This field represents the 5 bit PHY Address field of Mgmt

cycles. Up to 31 PHYs can be addressed (0 is reserved).

0x0

31:13

-

Unused

0x0

Table 200. MII Mgmt Write Data register (MWTD - address 0xFFE0 002C) bit description

Bit

Symbol

Function

Reset

value

15:0

WRITE

DATA

When written, an MII Mgmt write cycle is performed using the 16 bit

data and the pre-configured PHY and Register addresses from the

MII Mgmt Address register (MADR).

0x0

31:16

-

Unused

0x0

Table 201. MII Mgmt Read Data register (MRDD - address 0xFFE0 0030) bit description

Bit

Symbol

Function

Reset

value

15:0

READ

DATA

Following an MII Mgmt Read Cycle, the 16 bit data can be read from

this location.

0x0

31:16

-

Unused

0x0