2 usb device communication area, 3 triggering the dma engine, Refer to – NXP Semiconductors LPC24XX UM10237 User Manual

Page 375: Section 13–14.2 “usb device, Communication area, Section 13–14.2 “usb device communication area, Section 13–14.3, Triggering the dma engine, Nxp semiconductors

UM10237_4

© NXP B.V. 2009. All rights reserved.

User manual

Rev. 04 — 26 August 2009

375 of 792

NXP Semiconductors

UM10237

Chapter 13: LPC24XX USB device controller

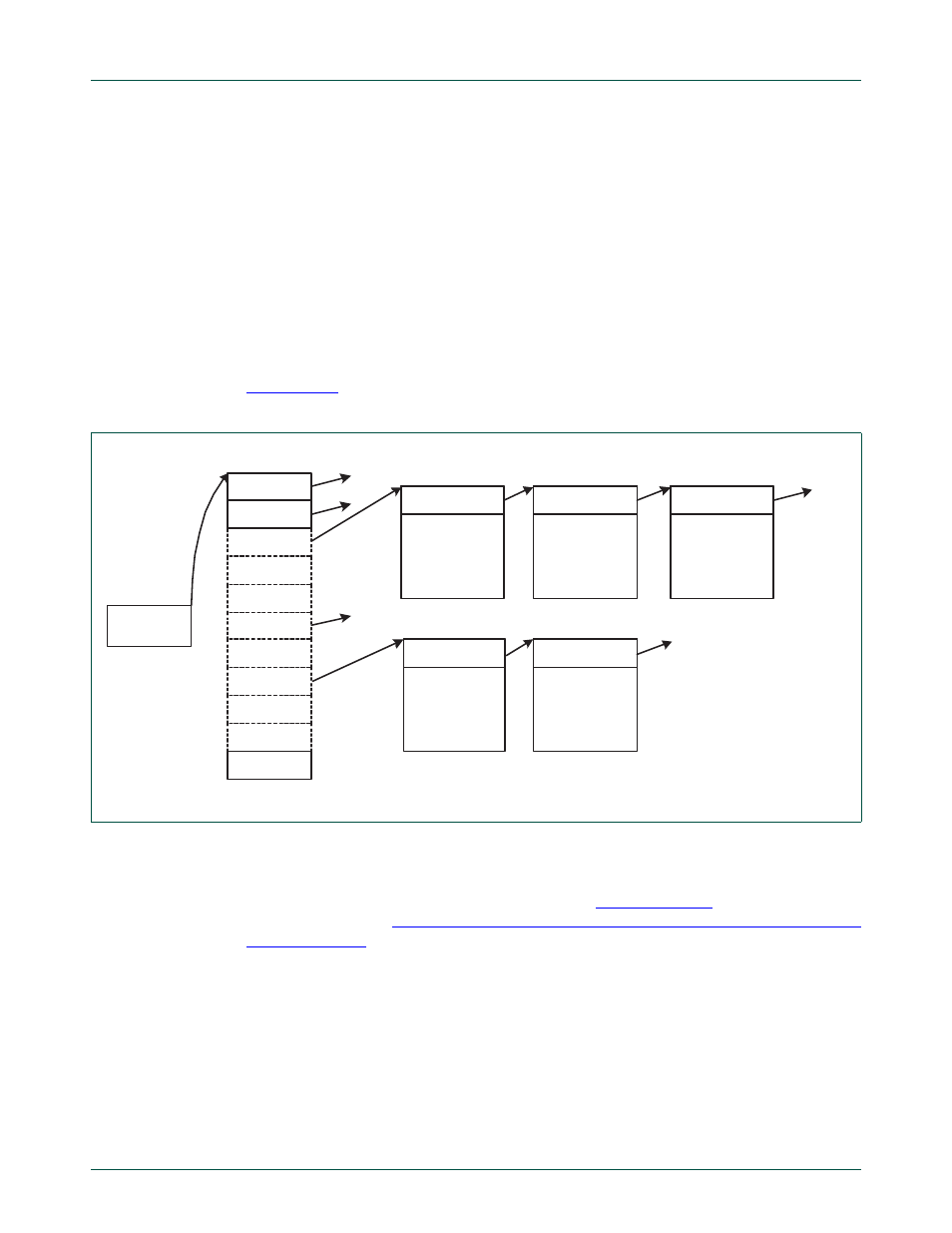

14.2 USB device communication area

The CPU and DMA controller communicate through a common area of memory, called the

USB Device Communication Area, or UDCA. The UDCA is a 32-word array of DMA

Descriptor Pointers (DDPs), each of which corresponds to a physical endpoint. Each DDP

points to the start address of a DMA Descriptor, if one is defined for the endpoint. DDPs

for unrealized endpoints and endpoints disabled for DMA operation are ignored and can

be set to a NULL (0x0) value.

The start address of the UDCA is stored in the USBUDCAH register. The UDCA can

reside at any 128-byte boundary of RAM that is accessible to both the CPU and DMA

controller.

illustrates the UDCA and its relationship to the UDCA Head (USBUDCAH)

register and DMA Descriptors.

14.3 Triggering the DMA engine

An endpoint raises a DMA request when Slave mode is disabled by setting the

corresponding bit in the USBEpIntEn register to 0 (

) and an endpoint

Section 13–9.8.1 “USB DMA Request Status register (USBDMARSt

).

A DMA transfer for an endpoint starts when the endpoint is enabled for DMA operation in

USBEpDMASt, the corresponding bit in USBDMARSt is set, and a valid DD is found for

the endpoint.

All endpoints share a single DMA channel to minimize hardware overhead. If more than

one DMA request is active in USBDMARSt, the endpoint with the lowest physical endpoint

number is processed first.

Fig 48. UDCA Head register and DMA Descriptors

UDCA HEAD

REGISTER

1

31

DDP-EP2

2

DD-EP2-a

NULL

NULL

Next_DD_pointer

0

NULL

DDP-EP31

NULL

DDP-EP16

16

NULL

DD-EP2-b

Next_DD_pointer

DD-EP2-c

Next_DD_pointer

DD-EP16-a

Next_DD_pointer

DD-EP16-b

Next_DD_pointer

UDCA