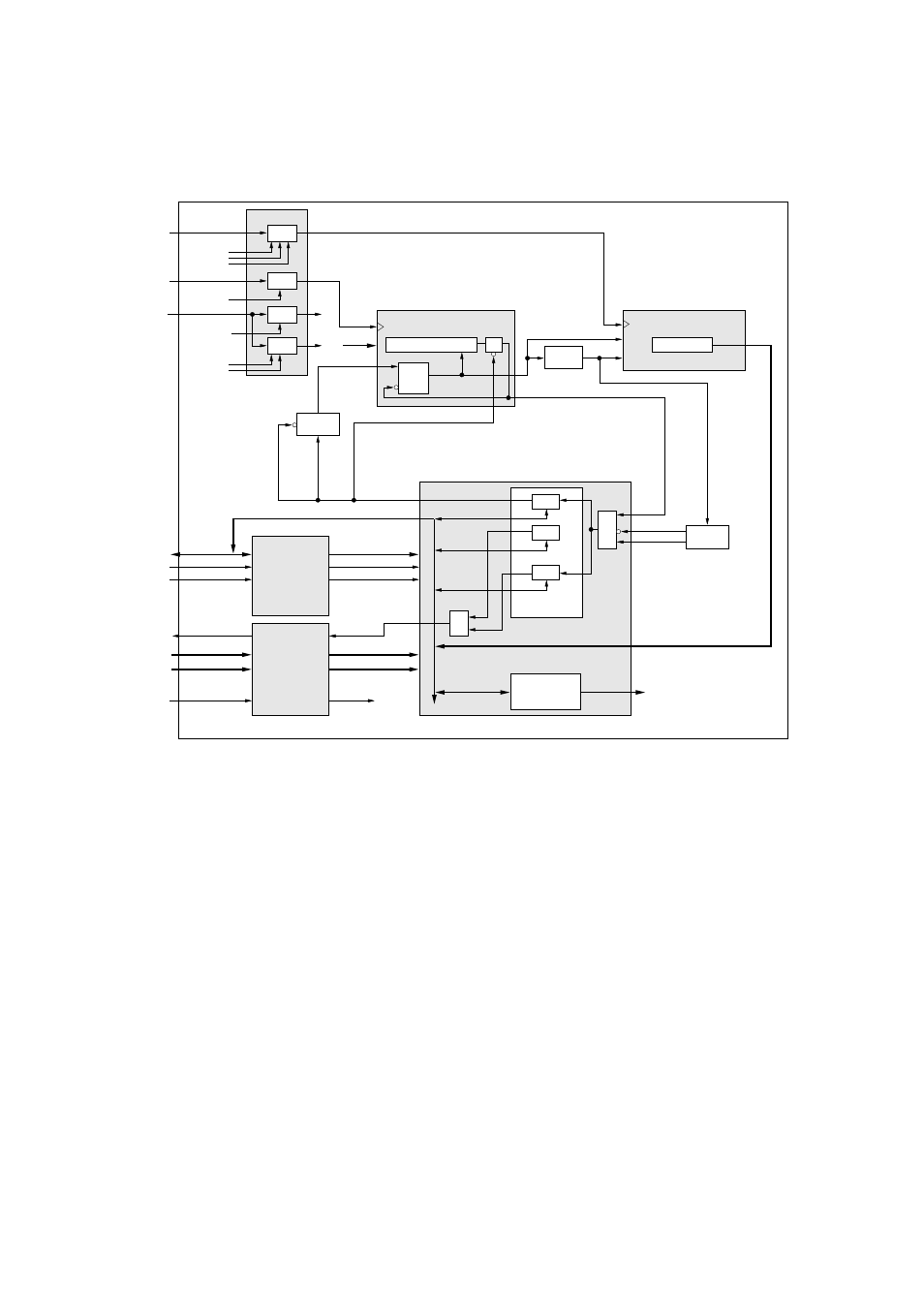

Block diagram, Figure 2-1 block diagram of the calibration unit – FUJITSU MB91460 SERIES FR60 User Manual

Page 980

964

Chapter 50 Subclock Calibration Unit

2.Block Diagram

2. Block Diagram

Figure 2-1 Block Diagram of the calibration unit

CLKPG2 = CLKP | (~STRT & RSLEEPB);

CLK4G = OSC4 | ~STRT | (READY & ~RUNS);

UC18CLK

RUN

RUN

READYPULSE

RUNS

RUNS

RUNSS1

&

&

STRT

sync

4->CLKP

sync

32->4

CLKP->32

sync

4MHz

TIMER

UC18TRR

CUTR

32kHz

TIMER

UC18TRD

UC18RBI

CUTR (24 bit)

UC18IO

UC18BUS

RBB

RSLEEPB

RMWB

*_WRB

*_RDB

RSTB

FC18

CLK32G

CUTD

RB

INT_I

CUTD

CUTD (16 bit)

CUCR (3 bit)

CUTR (24 bit)

INT_INT

set / reset

reset

set / reset

reset

READY

RUNSS

&

set

STRT

async

RST

INT

counter (16 bit)

READY

RST

async

READY

STRT

CLKPG2

RSLEEPB

RSLEEPB

RB

RSLEEP

RMW

*_WR

*_RD

RST

INT

CLKP

CLKPG

gate

gate

gate

STRT

gate

STRT

READY

CLK4G

INTEN

STRT

STRT

STRTS

OSC32

OSC4

See also other documents in the category FUJITSU Hardware:

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (76 pages)

- T5140 (102 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)