4 how do i set the operation clock division ratios – FUJITSU MB91460 SERIES FR60 User Manual

Page 219

203

Chapter 13 Clock Control

7.Q & A

7.4 How do I set the operation clock division ratios?

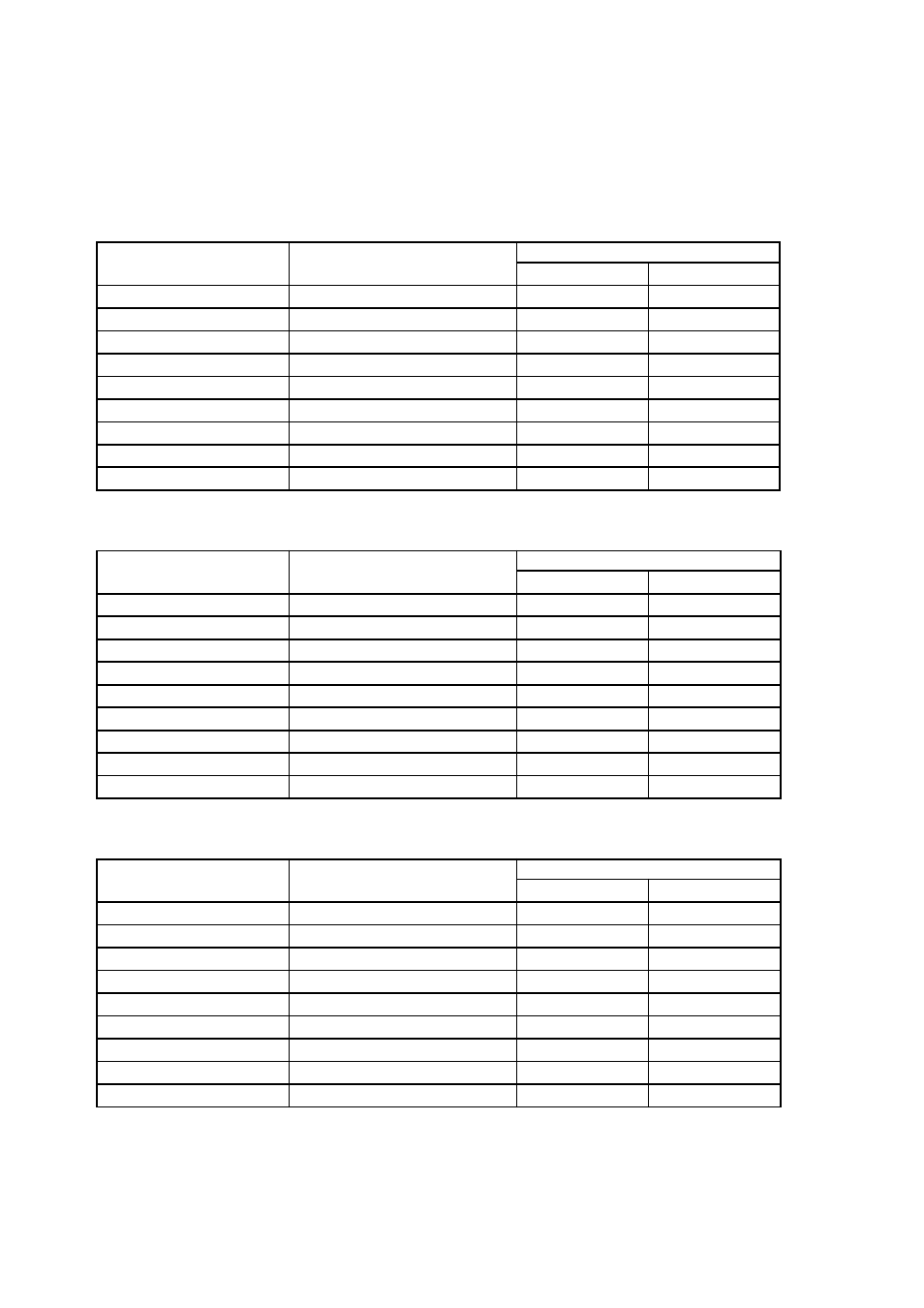

• CPU clock setting

The CPU clock setting is set using the CLKB division ratio selection bits (DIVR0.B[3:0]).

• Peripheral clock setting

The peripheral clock setting is set using the CLKP division ratio selection bits (DIVR0.P[3:0]).

• Setting for the external bus clock

The setting for the external bus clock is set using the CLKT division ratio selection bits (DIVR1.T[3:0]).

PLL multiplier ratio

CLKB division ratio selection

bits(B[3:0])

Example frequency

When F

Φ

= 32MHz

When F

Φ

= 16MHz

To select no division

Set to “0000”.

F

CLKB

= 32.0MHz

F

CLKB

= 16.0MHz

To select divide by 2

Set to “0001”.

F

CLKB

= 16.0MHz

F

CLKB

= 8.00MHz

To select divide by 3

Set to “0010”.

F

CLKB

= 10.6MHz

F

CLKB

= 5.33MHz

To select divide by 4

Set to “0011”.

F

CLKB

= 8.00MHz

F

CLKB

= 4.00MHz

To select divide by 5

Set to “0100”.

F

CLKB

= 6.40MHz

F

CLKB

= 3.20MHz

To select divide by 6

Set to “0101”.

F

CLKB

= 5.33MHz

F

CLKB

= 2.66MHz

To select divide by 7

Set to “0110”.

F

CLKB

= 4.57MHz

F

CLKB

= 2.28MHz

To select divide by 8

Set to “0111”.

F

CLKB

= 4.00MHz

F

CLKB

= 2.00MHz

To select divide by 16

Set to “1111”.

F

CLKB

= 2.00MHz

F

CLKB

= 1.00MHz

PLL multiplier ratio

CLKP division ratio selection bits

(P[3:0])

Example frequency

When F

Φ

= 32MHz

When F

Φ

= 16MHz

To select no division

Set to “0000”.

F

CLKP

= 32.0MHz

F

CLKP

= 16.0MHz

To select divide by 2

Set to “0001”.

F

CLKP

= 16.0MHz

F

CLKP

= 8.00MHz

To select divide by 3

Set to “0010”.

F

CLKP

= 10.6MHz

F

CLKP

= 5.33MHz

To select divide by 4

Set to “0011”.

F

CLKP

= 8.00MHz

F

CLKP

= 4.00MHz

To select divide by 5

Set to “0100”.

F

CLKP

= 6.40MHz

F

CLKP

= 3.20MHz

To select divide by 6

Set to “0101”.

F

CLKP

= 5.33MHz

F

CLKP

= 2.66MHz

To select divide by 7

Set to “0110”.

F

CLKP

= 4.57MHz

F

CLKP

= 2.28MHz

To select divide by 8

Set to “0111”.

F

CLKP

= 4.00MHz

F

CLKP

= 2.00MHz

To select divide by 16

Set to “1111”.

F

CLKP

= 2.00MHz

F

CLKP

= 1.00MHz

PLL multiplier ratio

CLKT division ratio selection bits

(T[3:0])

Example frequency

When F

Φ

= 32MHz

When F

Φ

= 16MHz

To select no division

Set to “0000”.

F

CLKT

= 32.0MHz

F

CLKT

= 16.0MHz

To select divide by 2

Set to “0001”.

F

CLKT

= 16.0MHz

F

CLKT

= 8.00MHz

To select divide by 3

Set to “0010”.

F

CLKT

= 10.6MHz

F

CLKT

= 5.33MHz

To select divide by 4

Set to “0011”.

F

CLKT

= 8.00MHz

F

CLKT

= 4.00MHz

To select divide by 5

Set to “0100”.

F

CLKT

= 6.40MHz

F

CLKT

= 3.20MHz

To select divide by 6

Set to “0101”.

F

CLKT

= 5.33MHz

F

CLKT

= 2.66MHz

To select divide by 7

Set to “0110”.

F

CLKT

= 4.57MHz

F

CLKT

= 2.28MHz

To select divide by 8

Set to “0111”.

F

CLKT

= 4.00MHz

F

CLKT

= 2.00MHz

To select divide by 16

Set to “1111”.

F

CLKT

= 2.00MHz

F

CLKT

= 1.00MHz