6 clear timing – FUJITSU MB91460 SERIES FR60 User Manual

Page 869

853

Chapter 41 Up/Down Counter

5.Operation

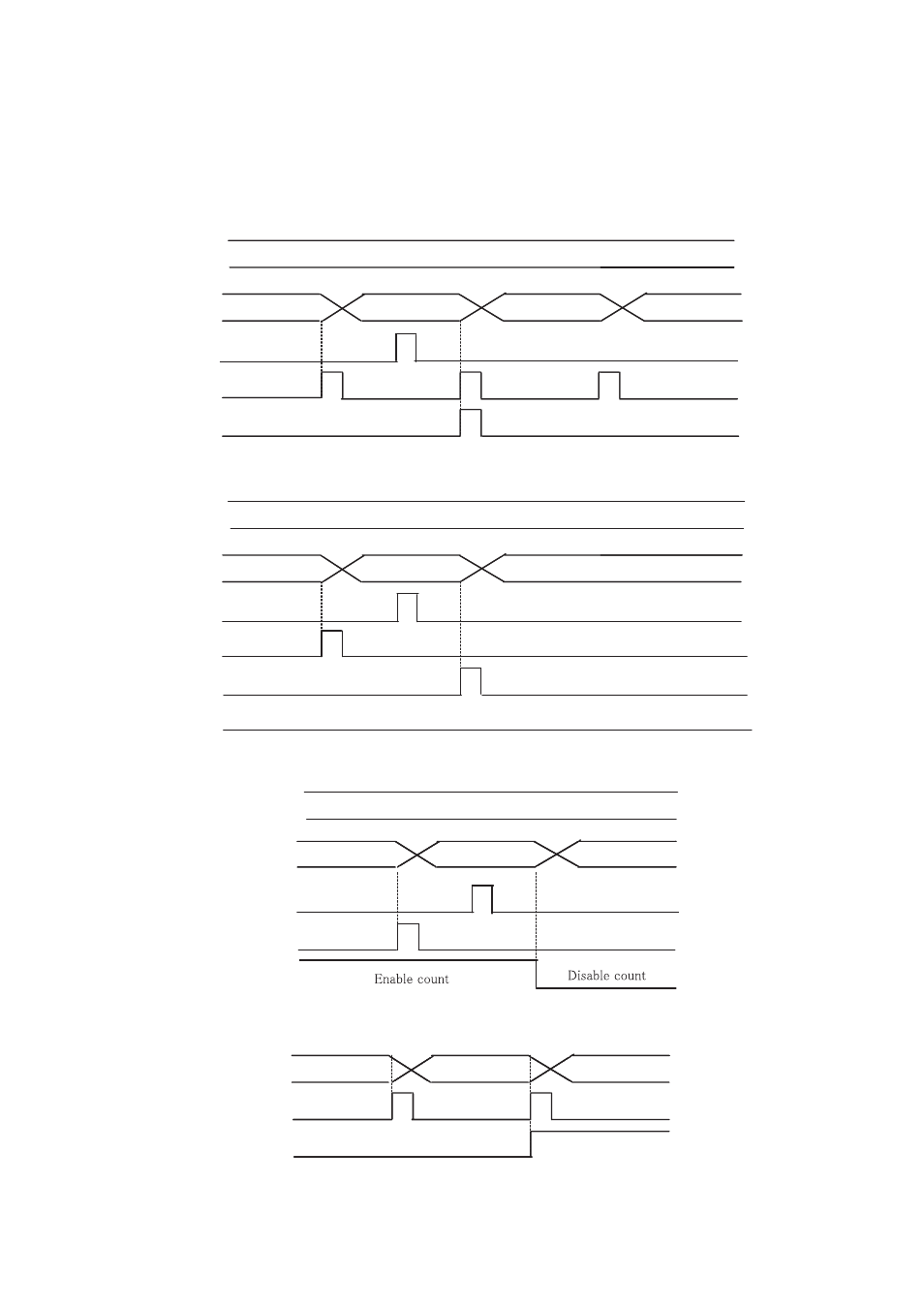

5.6 Clear Timing

(1) When a clear request (Compare-match, ZIN edge detection and writing “0” to the clear bit UDCLR) is

made, clear is performed next time when Up/Down Counter counts up.

(2) Even if a clear request (Compare-match, ZIN edge detection and writing “0” to the clear bit DCC) is made,

clear is not performed when UP/Down Counter counts neither up nor down.

(3) If Up/Down Counter does not count up after a clear request (Compare-match, ZIN edge detection and

writing “0” to the clear bit DCC) is made, the counter is cleared when counting is disabled (CSTR=“0”).

(4) When Up/Down Counter exceeds the maximum count, the overflow flag is set to “1” and the counter value

is returned to “0000”.

0066

H

0065

H

0066

H

0000

H

Clear request

Countup

Clear timing

0001

H

Count value

Compare value

0066

H

0065

H

0066

H

0065

H

Countup

Clear timing (None)

Countdown

Clear request

Count value

Compare value

H

Clear request

0066

H

Countup

CSTR or ZIN gate function

0065

H

0066

H

0000

H

Count value

Compare value

Overflow

Countup

FFFEH

FFFFH

0000

Count value

FFFEH

FFFFH

0000

H