FUJITSU MB91460 SERIES FR60 User Manual

Page 354

338

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

[Bits 28 to 24] IS4 to 0 (Input Select)*: Transfer source selection

These bits select the source of a transfer request note that the software transfer request by the STRG bit

function is always valid regardless of the setting of these bits. As listed in

"Settings for Transfer

Request Sources".

•

When reset: IS4-0 is initialized to 00000

B

.

•

When reset: EIS3-0 is initialized to 0000

B

.

•

These bits are readable and writable.

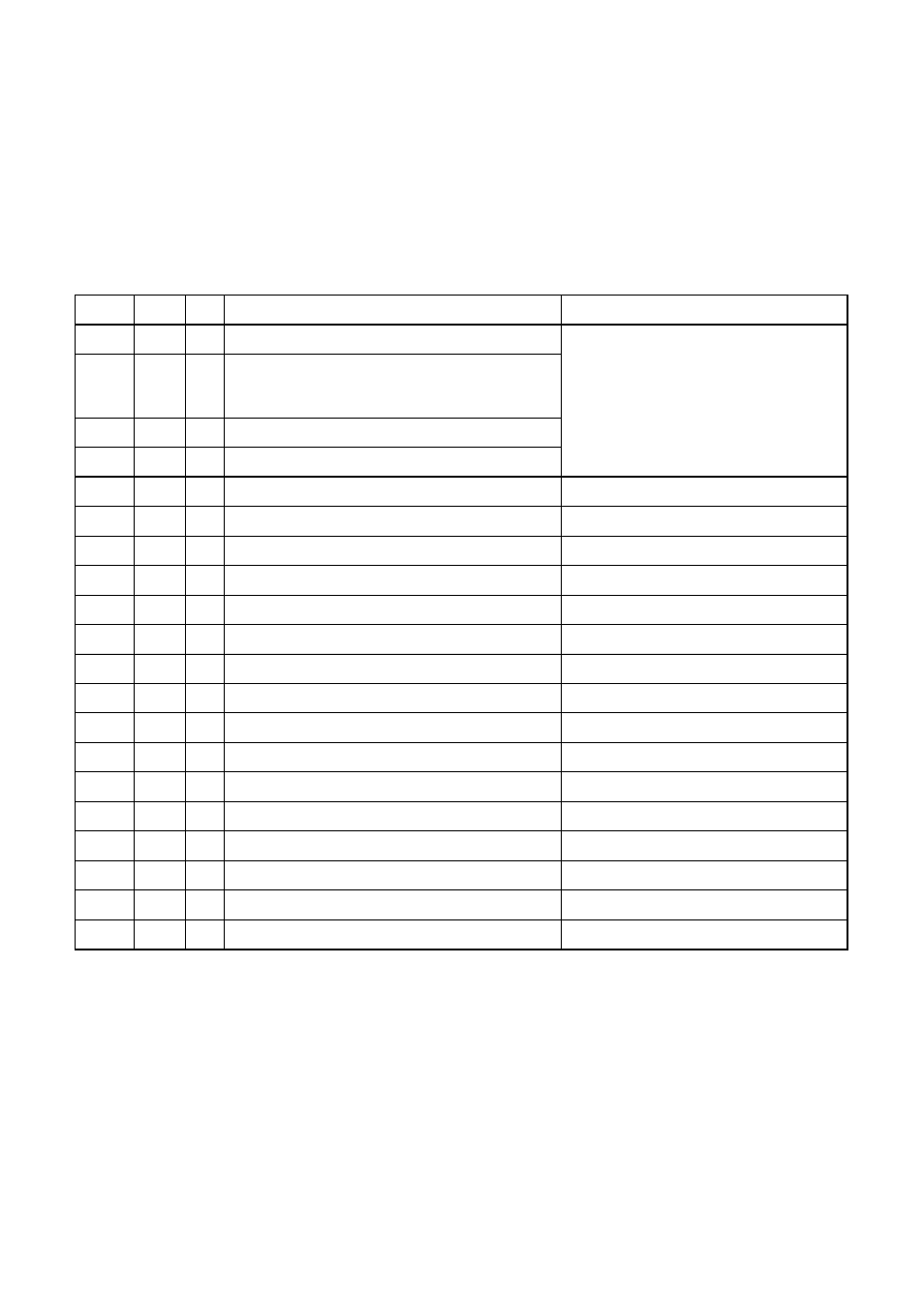

Table 2-1 Settings for Transfer Request Sources

IS

EIS

RN

Function

Transfer stop request

00000

-

-

Activation by hardware prohibited

not available

00001

-

01101

-

-

Setting prohibited

-

Setting prohibited

01110

-

-

External DMA-pin high level or rising edge

01111

-

-

External DMA-pin low level or falling edge

10000

0000

0

External Interrupt 0

-

10001

0000

1

External Interrupt 1

-

10010

0000

2

External Interrupt 2

-

10011

0000

3

External Interrupt 3

-

10100

0000

4

Reload Timer 0

-

10101

0000

5

Reload Timer 1

-

10110

0000

6

USART (LIN) 0 RX

available

10111

0000

7

USART (LIN) 0 TX

-

11000

0000

8

USART (LIN) 1 RX

available

11001

0000

9

USART (LIN) 1 TX

-

11010

0000

10

USART (LIN, FIFO) 4 RX

available

11011

0000

11

USART (LIN, FIFO) 4 TX

-

11100

0000

12

USART (LIN, FIFO) 5 RX

available

11101

0000

13

USART (LIN, FIFO) 5 TX

-

11110

0000

14

A/D Converter

-

11111

0000

15

Programmable Pulse Generator (PPG) 0

-