Registers, 1 tmcsr: reload timer control status register – FUJITSU MB91460 SERIES FR60 User Manual

Page 794

778

Chapter 38 Reload Timer

4.Registers

4. Registers

4.1 TMCSR: Reload Timer Control Status Register

The control status register controls the operation mode of the reload timer and interrupts.

• TMCSR0 (Reload timer 0): Address: 001B6H (Access:

Byte, Half-word

)

• TMCSR1 (Reload timer 1): Address: 001BEH (Access:

Byte, Half-word

)

• TMCSR2 (Reload timer 2): Address: 001C6H (Access:

Byte, Half-word

)

• TMCSR3 (Reload timer 3): Address: 001CEH (Access:

Byte, Half-word

)

• TMCSR4 (Reload timer 4): Address: 001D6H (Access:

Byte, Half-word

)

• TMCSR5 (Reload timer 5): Address: 001DEH (Access:

Byte, Half-word

)

• TMCSR6 (Reload timer 6): Address: 001E6H (Access:

Byte, Half-word

)

• TMCSR7 (Reload timer 7): Address: 001EEH (Access:

Byte, Half-word

)

(O: can be rewritten, x: cannot be rewritten)

(For information on attributes, see “

Meaning of Bit Attribute Symbols (Page No.10)

• bit15-14: Undefined

Writing has no effect on the operation. The read value is “0”.

• bit13: Undefined (reload timer 0 - reload timer 2)

Always write “0”. The read value is “0”.

• bit12-10: Count clock selection CLKP: peripheral clock

Notes:

Depending on whether an internal clock or an external event is selected, the meaning of

the operation mode selection bit (MOD[2:0]) changes.

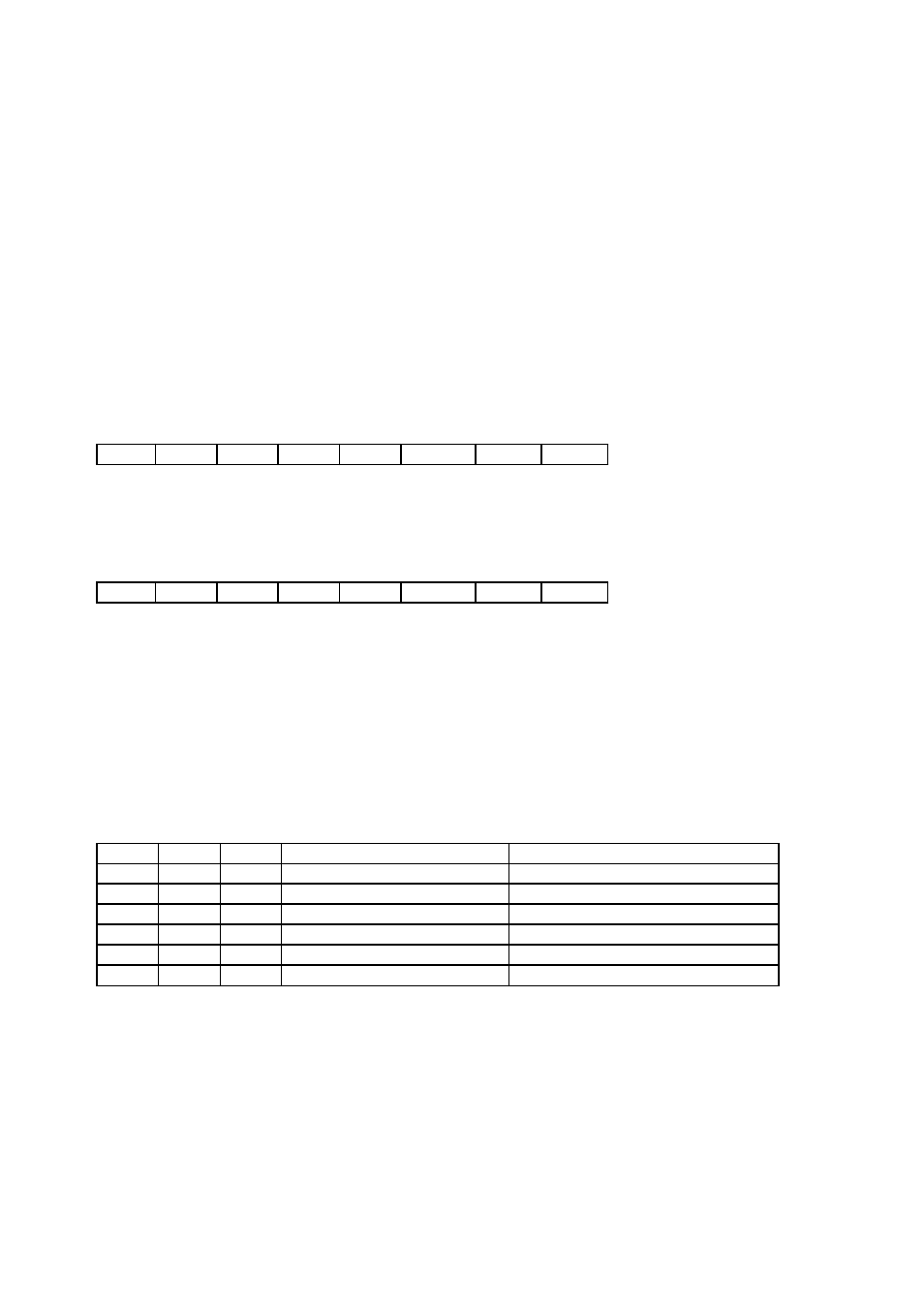

15

14

13

12

11

10

9

8

bit

–

–

–

CSL2

CSL1

CSL0

MOD2

MOD1

-

-

-

0

0

0

0

0

Initial Value

RX/WX

RX/WX

RX/WX

R0/WX

R/W

R/W

R/W0

R/W

Attribute

Ч

Ч

Ч

Ч

Ч

Ч

Ч

Ч

Rewrite during

operation

7

6

5

4

3

2

1

0

bit

MOD0

–

OULT

RELD

INTE

UF

CNTE

TRG

0

-

0

0

0

0

0

0

Initial Value

R/W

RX/WX

R/W

R/W

R/W

R(RM1),W

R/W

R0/W

Attribute

Ч

–

Ч

Ч

Ч

Ο

Ο

Ο

Rewrite during

operation

CSL2

CSL1

CSL0

Count clock

Remarks

0

0

0

Internal clock CLKP/2

0

0

1

Internal clock CLKP/8

0

1

0

Internal clock CLKP/32

0

1

1

External event (external clock)

1

0

1

Internal clock CLKP/64

1

1

0

Internal clock CLKP/128