Operating mode conditions, Cache status in various operating modes – FUJITSU MB91460 SERIES FR60 User Manual

Page 201

185

Chapter 12 Instruction Cache

3.Operating mode conditions

3. Operating mode conditions

●

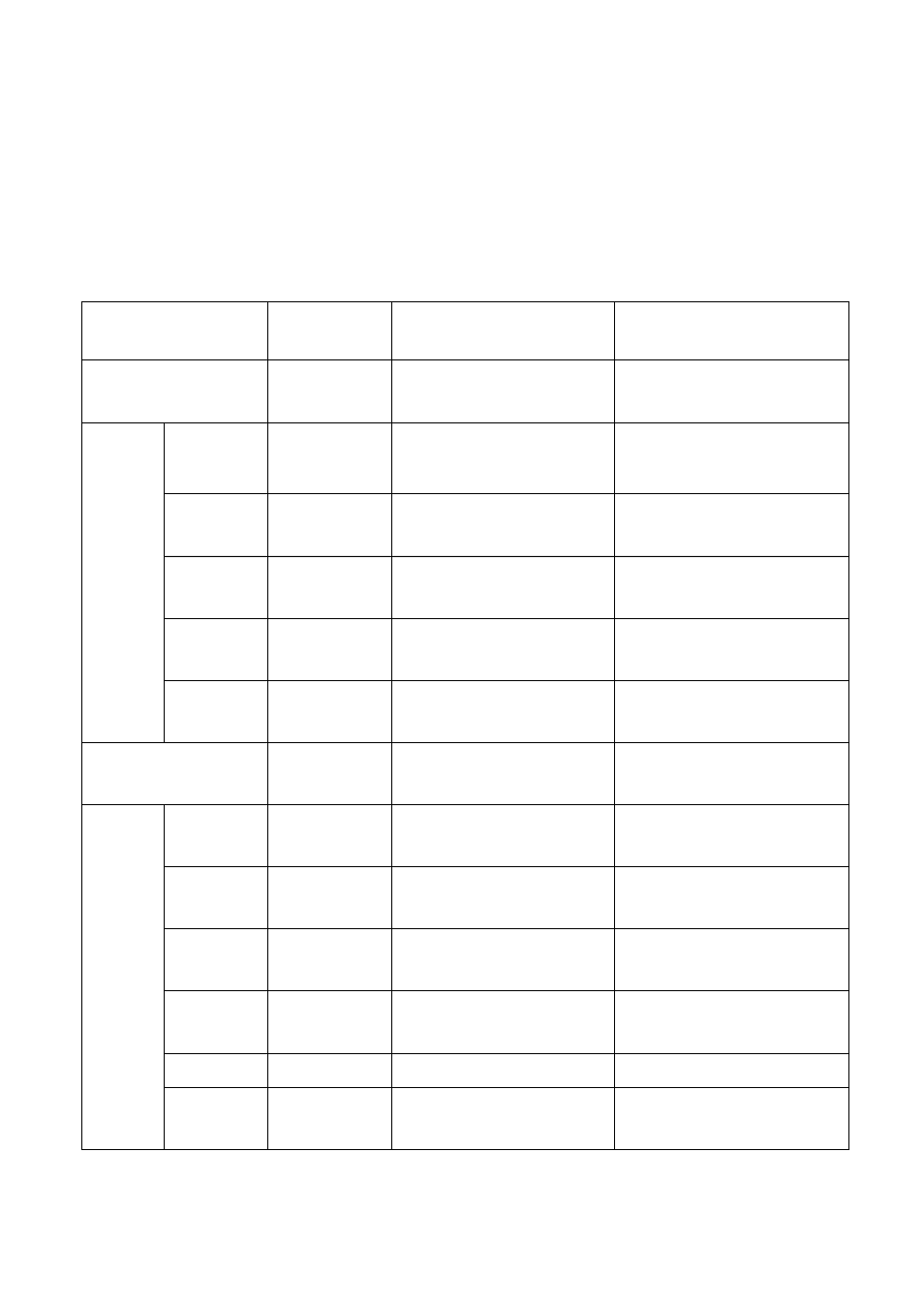

Cache status in various operating modes

The table below indicates the prevailing state for disable and flush when the associated bit is

changed by bit manipulation instruction, etc.

Immediately

after a Reset

Disable (FNAB=0)

Flushed

Cache Memory

Contents

undefined

The preceding state is held.

Rewriting is impossible while

the cache is disabled.

The preceding state is held.

Tag

Address

Tag

Contents

undefined

The preceding state is held.

Rewriting is impossible while

the cache is disabled.

The preceding state is held.

Sub-block

Valid Bit

Contents

undefined

The preceding state is held.

Rewriting is impossible while

the cache is disabled.

The preceding state is held.

LRU Bit

Contents

undefined

The preceding state is held.

Rewriting is impossible while

the cache is disabled.

The preceding state is held.

Entry Lock

Bit

Contents

undefined

The preceding state is held.

Rewriting is impossible while

the cache is disabled.

The preceding state is held.

(entry lock release is required)

TAG Valid

Bit

Contents

undefined

The preceding state is held.

Flushingis possible while the

cache is disabled.

All entries are invalid.

RAM

Normal Mode

The preceding state is held.

Flushing is possible while

the cache is disabled.

The preceding state is held.

Control

Register

Global

Lock

Unlock

The preceding state is held.

Rewriting is possible while

the cache is disabled.

The preceding state is held.

Auto lock

Fail

No fail

The preceding state is held.

Rewriting is possible while

the cache is disabled.

The preceding state is held.

Entry Auto

Lock

Unlock

The preceding state is held.

Rewriting is possible while

the cache is disabled.

The preceding state is held.

Entry Lock

Release

No release

The preceding state is held.

Rewriting is possible while

the cache is disabled.

The preceding state is held.

Enable

Disable

Disabled

The preceding state is held.

Flush

Not flushed

The preceding state is held.

Rewriting is possible while

the cache is disabled.

Flushed in cycle following

memory accessing.

Reverts to 0 subsequently.