Configuration, Chapter 49 real-time clock 3.configuration, 21 bit counter – FUJITSU MB91460 SERIES FR60 User Manual

Page 966: Wtbr wtsr, Wtmr, Wthr, Wtsr

950

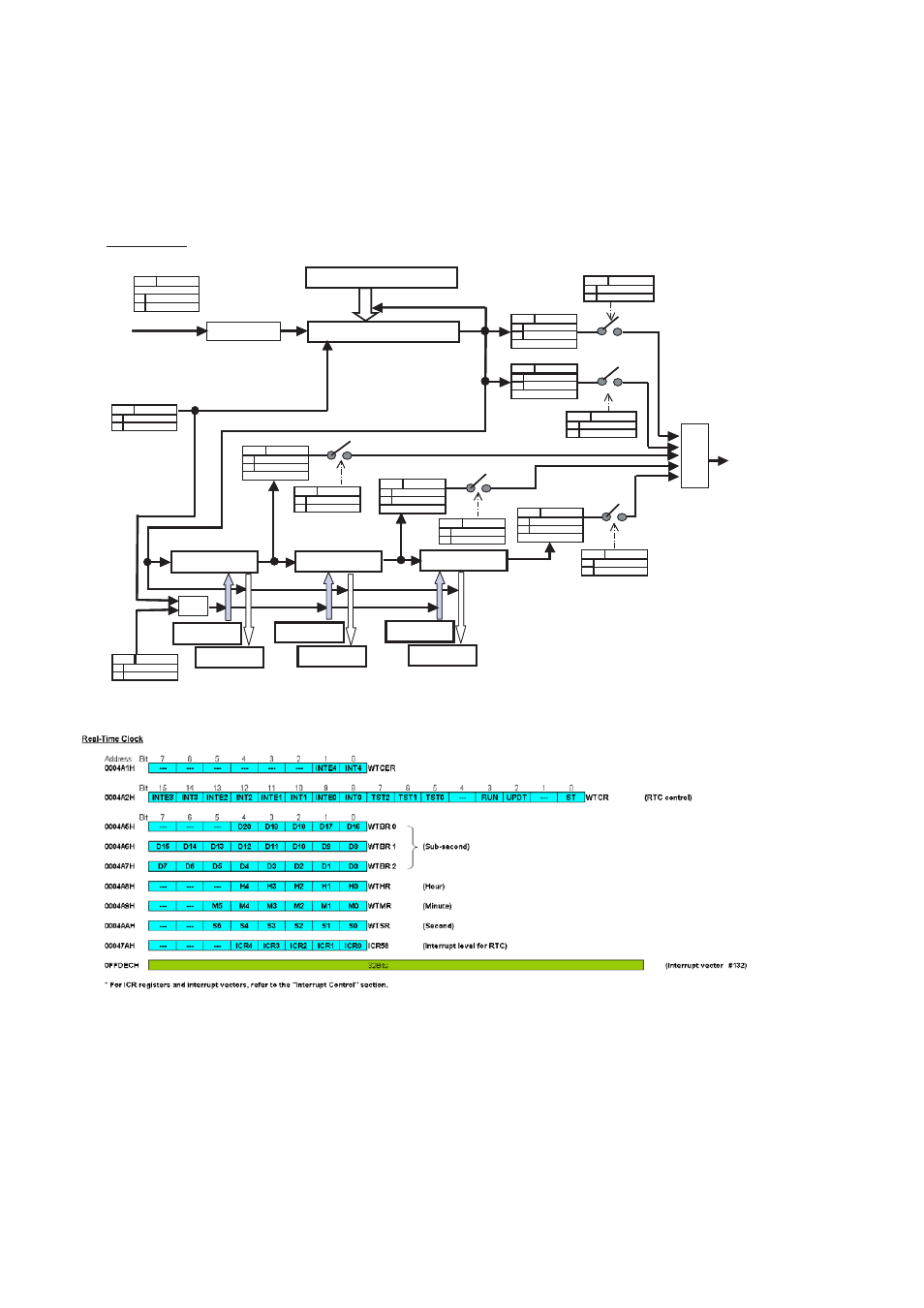

Chapter 49 Real-Time Clock

3.Configuration

3. Configuration

Figure 3-1 Configuration Diagram

Figure 3-2 Register List

Note: For ICR registers and interrupt vectors, refer to “

Chapter 24 Interrupt Control (Page No.311)

21 Bit Counter

INTE1 WT CR: bit11

0

1

WTBR

WTSR

(W)

WTMR

(W)

WTHR

(W)

INT1 WT CR: bit10

0

1

Read: 1=

INT2 WT CR: bit12

0

1

Read: 1=

INTE2 WT CR: bit13

0

1

INT3 WT CR: bit14

0

1

Read: 1=

INTE3 WT CR: bit15

0

1

Disable interrupts

Enable interrupts

RTC

interrupt

(#132)

Overflow

INT4

WT CER: bit0

0

1

INTE4

WT CER: bit9

0

1

Disable interrupts

Enable interrupts

Every half second

Every minute

Every 24 hour (Everyday)

Every hour

Second

Minute

Hour

ST

WT CR: bit 0

0

1

OR

0

1

1

1

1

0

0

0

WTBR value = 1/2 second

(Initial value indeterminate)

UPDT

0

1

WT CR: bit 2

No impact on operation

Update

RUN WT CR: bit 3

0

Read

RT C

1

RT C

Real-Time Clock

Overflow

Overflow

WTSR

(R)

WTMR

(R)

WTHR

(R)

OR

Prescaler: 1/2

INTE1 WT CR: bit11

0

1

INTE1 WT CR: bit11

0

1

Disable interrupts

Enable interrupts

Reload

Second Counter

Minute Counter

Hour Counter

INT1 WT CR: bit10

0

1

Read: 1=

INT1 WT CR: bit10

0

1

Disable

Read: 1=Interrupt request has been made

Read: 1=Interrupt request has been made

INT2 WT CR: bit12

0

1

Read: 1=

INT2 WT CR: bit12

0

1

Disable

Disable

INTE2 WT CR: bit13

0

1

INTE2 WT CR: bit13

0

1

Disable interrupts

Enable interrupts

INT3 WT CR: bit14

0

1

Read: 1=

INT3 WT CR: bit14

0

1

Clear interrupt requests

Clear interrupt requests

Clear interrupt requests

Clear interrupt requests

Disable

ST

WT CR: bit 0

0

1

ST

WT CR: bit 0

0

1

Stop after reset

Start

0

1

RUN WT CR: bit 3

0

Read

RT C

1

RT C

RUN WT CR: bit 3

0

Read only

RTC inactive

1

RTC active

Read: 1=Interrupt request has been made

Read: 1=Interrupt request has been made

OR

INT0 WT CR: bit8

0

1

INTE0 WT CR: bit9

0

1

Disable interrupts

Enable interrupts

Every second

0

1

Read: 1=Interrupt request has been made

Disable

Clear interrupt requests

Oscillation