11 what interrupt registers are used, 12 what interrupts are available, 13 how do i enable, disable, clear interrupts – FUJITSU MB91460 SERIES FR60 User Manual

Page 921

905

Chapter 44 A/D Converter

6.Q & A

6.11 What interrupt registers are used?

A/D interrupt vector, A/D interrupt level setting

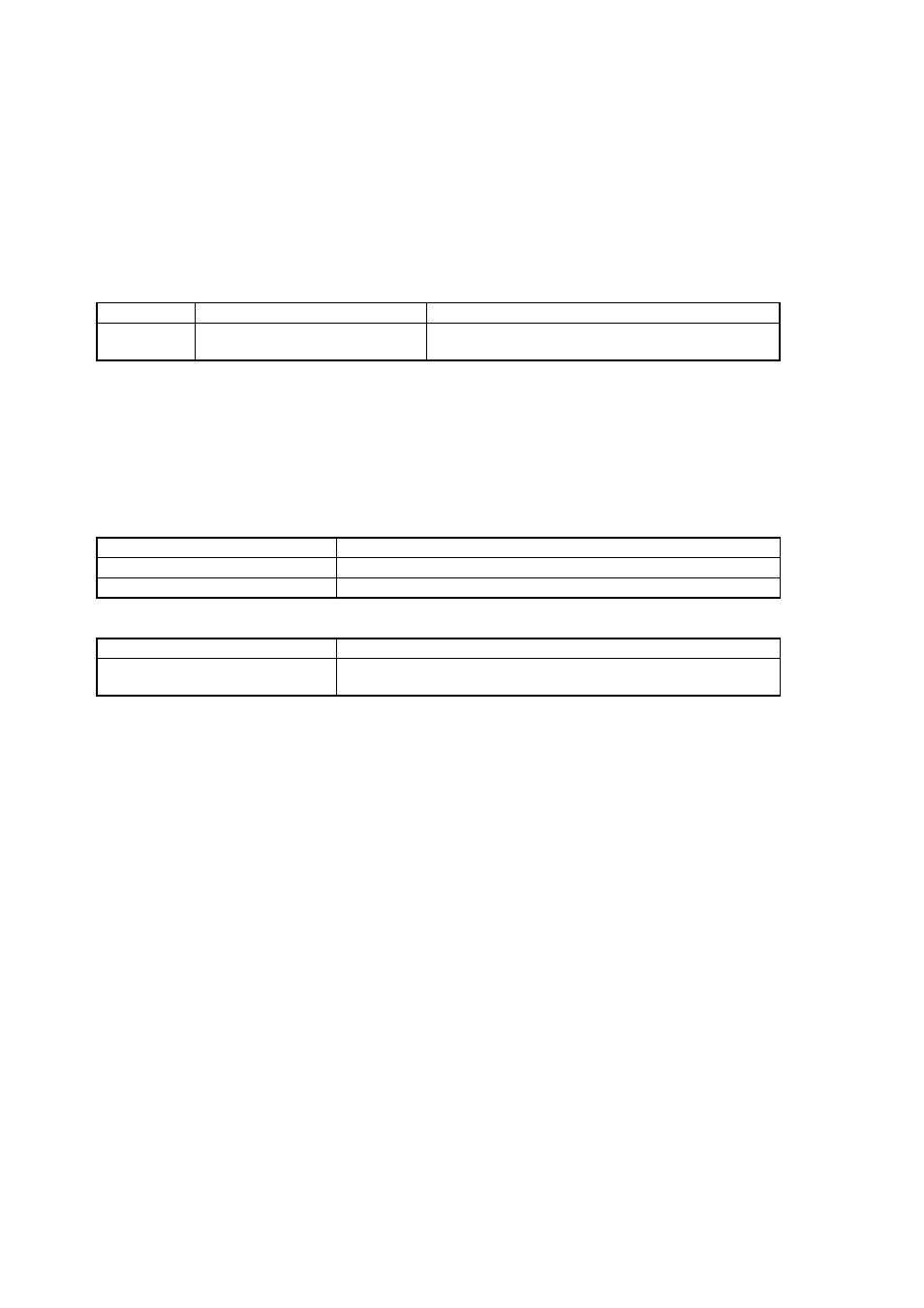

The table below summarizes the relationships among the machine cycle, A/D number, interrupt level, and

interrupt vector.

For more information about the interrupt level and interrupt vector, see “

Chapter 24 Interrupt Control (Page

.”

6.12 What interrupts are available?

A/D Conversion End interrupt only. No interrupt cause selection bit is available.

6.13 How do I enable, disable, clear interrupts?

Interrupt Request Enable flag, Interrupt Request flag

Interrupts are enabled using the Interrupt Request Enable bits (ADCS.INTE).

Interrupt request are cleared using the Interrupt Request bits (ADCS.INT).

(See “

”.)

Interrupt Vector (Default)

Interrupt Level Setting Bit (ICR[4:0])

AD0

#134

Address: 0FFDE4h

Interrupt Level register (ICR59)

Address: 047Bh

Interrupt Request Enable Bit (INTE)

To disable interrupt requests

Set “0”.

To enable interrupt requests

Set “1”.

Interrupt Request Bit (INT)

To clear interrupt requests

Write “0”

or activate A/D. (See “

6.7 To activate the A/D converter (Page No.904)

”.)