Q & a, 5 how do i reverse the output level – FUJITSU MB91460 SERIES FR60 User Manual

Page 805

789

Chapter 38 Reload Timer

7.Q & A

7. Q & A

7.1 What is the reload value setting (rewriting) procedure?

The reload value is set by the 16 bit reload registers TMRLR0-TMRLR7.

The equation for the values to be set is as follows.

• Formula

TMRLR register value = {reload interval/count clock}-1

• Allowed Range

TMRLR register value = 0~FFFh (65535)

7.2 What are the kinds of count clocks and how are they selected?

The count clock is chosen from the 4 types in the table below.

Selection is done via the count clock selection bit.

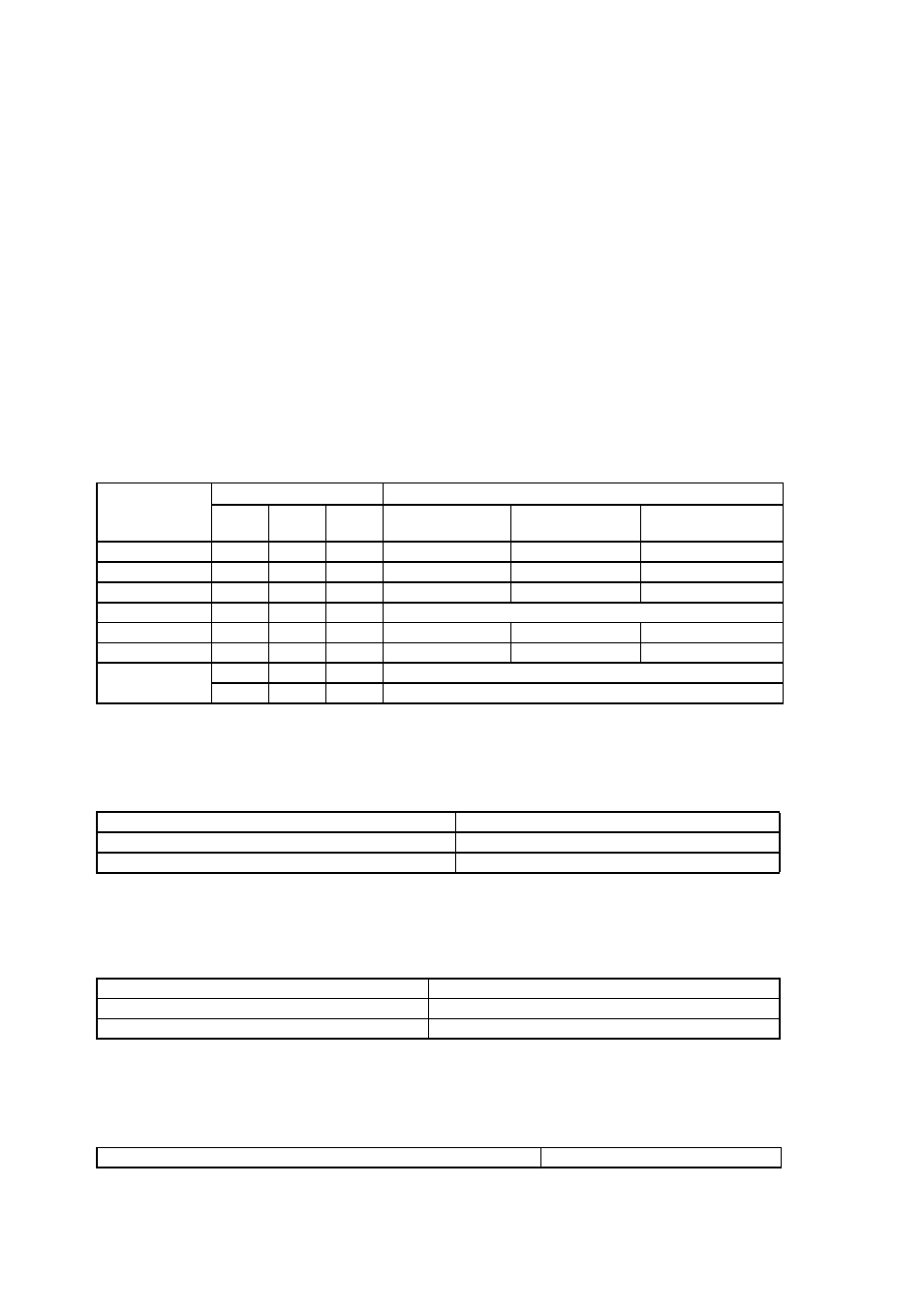

Table 7-1 TMCSR.CSL[2:0]

(*: See “

7.3 How to I enable/disable the reload timer count operation?

Use the timer count enable bit (TMCSR.CNTE).

Cannot be reopened from the stopped state. Enable before activation or simultaneous with activation.

7.4 How do I set the reload timer mode (reload/one-shot)?

Use mode selection bit (TMCSR.RELD).

7.5 How do I reverse the output level?

The settings for the output level are detailed in the following table.

The setting is done via timer output level bit (TMCSR.OUTL).

Count

Clock

Counter clock selection bit

Count clock example

CSL2

CSL1

CSL0

When CLKP=

32MHz

When CLKP=

16MHz

When CLKP= 8MHz

CLKP/2

0

0

0

62.5ns

125ns

250ns

CLKP/8

0

0

1

250ns

500ns

1.0

µs

CLKP/32

0

1

0

1.0

µs

2.0

µs

4.0

µs

External event

0

1

1

Pulse width: 2/CLKP min

CLKP/64

1

0

1

2.0

µs

4.0

µs

8.0

µs

CLKP/128

1

1

0

4.0

µs

8.0

µs

16.0

µs

Disabled *

1

0

0

-----

1

1

1

-----

Control Details

RLT operation permission bit (CNTE)

To stop the reload timer

Set to “0”

To enable the reload timer’s count operation

Set to “1”

Operation Mode

Mode selection bit (RELD)

To set to one-shot mode

Set to “0”

To set to reload

Set to “1”

Output level

Timer output level bit (OUTL)