FUJITSU MB91460 SERIES FR60 User Manual

Page 639

623

Chapter 32 USART (LIN / FIFO)

4.USART Registers

* see table

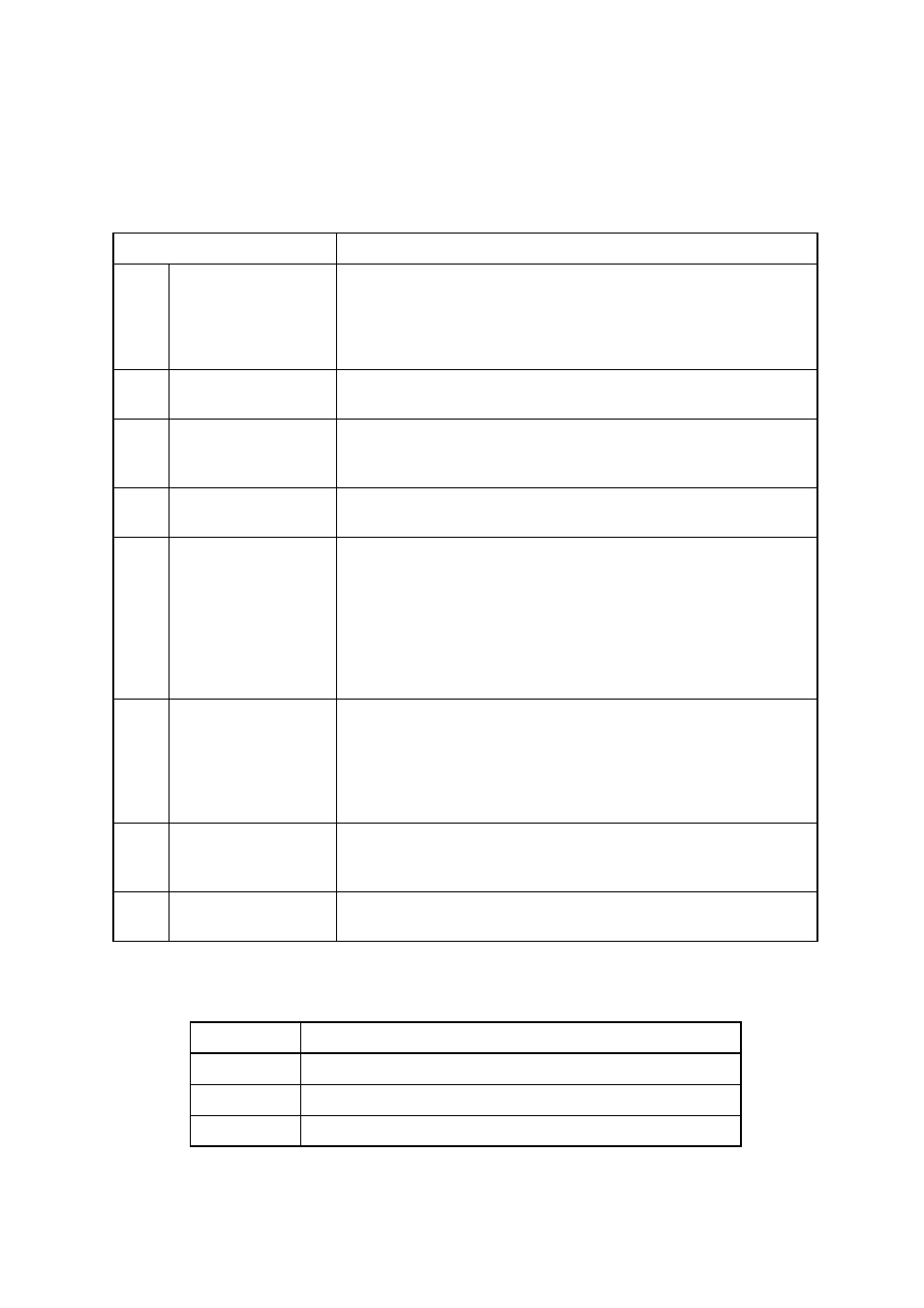

Table 4-2 Functions of each bit of control register 04 (SCR04)

Bit name

Function

bit15

PEN: Parity enable

bit

This bit selects whether to add a parity bit during transmission in

serial asynchronous mode or detect it during reception.

Parity is only provided in mode 0 and in mode 2 if SSM of the

ECCR04 is selected. This bit is fixed to 0 (no parity) in mode 3

(LIN).

bit14

P: Parity selection bit

When parity is provided and enabled this bit selects even (0) or

odd (1) parity

bit13

SBL: Stop bit length

selection bit

This bit selects the length of the stop bit of an asynchronous data

frame or a synchronous frame if SSM of the ECCR04 is selected.

This bit is fixed to 0 (1 stop bit) in mode 3 (LIN).

bit12

CL: Data length

selection bit

This bit specifies the length of transmission or reception data. This

bit is fixed to 1 (8 bits) in mode 2 and 3.

bit11

AD: Address/Data

selection bit *

This bit specifies the data format in multiprocessor mode 1. Writing

to this bit determines an address or data frame to be sent next,

reading from it returns the last received kind of frame. “1” indicates

an address frame, “0” indicates a usual data frame.

Note:

During a RMW-Read cycle the AD bit returns the value to be

sent instead of the last received AD bit.

see table below*

bit10

CRE: Clear reception

error flags bit

This bit clears the FRE, ORE, and PE flag of the Serial Status

Register (SSR04). This bit also clears a possible reception

interrupt caused by errors.

Writing a 1 to it clears the error flag.

Writing a 0 has no effect.

Reading from it always returns 0.

bit9

RXE: Reception

enable bit

This bit enables USART reception.

If this bit is set to 0, USART disables the reception of data frames.

The LIN break detection in mode 0 or 3 remains unaffected.

bit8

TXE: Transmission

enable bit

This bit enables USART transmission. If this bit is set to 0, USART

disables the transmission of data frames.

Table 4-3 * Read/Write options of AD-Bit

Cycle

Action

Write

Write data to be sent to AD-Bit

Normal Read

Read received AD-Bit

RMW-Read

Read data to be sent from AD-Bit