Register, 1 udcc: counter control register, Register 4.1 udcc: counter control register – FUJITSU MB91460 SERIES FR60 User Manual

Page 856

840

Chapter 41 Up/Down Counter

4.Register

4. Register

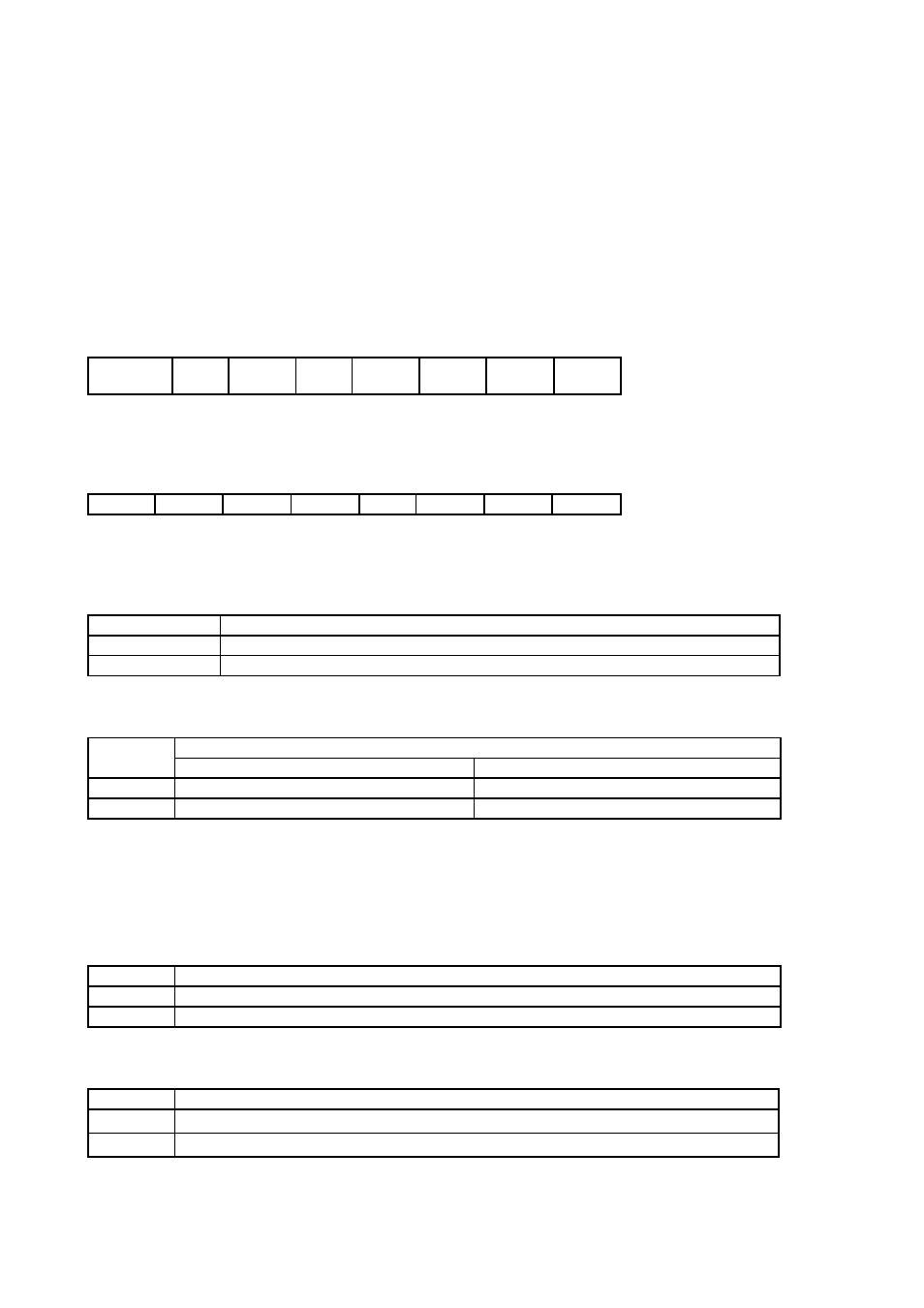

4.1 UDCC: Counter Control Register

This register is used to control behaviors of Up/Down Counter.

• UDCC0 (Up/Down Counter 0): Address 0304

H

(Access:

Byte, Half-word

)

• UDCC1 (Up/Down Counter 1): Address 0308

H

(Access:

Byte, Half-word

)

• UDCC2 (Up/Down Counter 2): Address 0314

H

(Access:

Byte, Half-word

)

• UDCC3 (Up/Down Counter 3): Address 0318

H

(Access:

Byte, Half-word

)

Meaning of Bit Attribute Symbols (Page No.10)

•

bit15: Enable 16 bit mode (Up/Down Counter

0

only)

* Reserved bit (Up/Down Counter 1 and 3). Be sure to write 0. The read value is the value written.

• bit14: Count direction change flag (Interrupt request flag)

• When the count direction has been changed during count operation, the count direction change flag

(CDCF) is set to “1”.

• Since the count direction is set to countdown immediately after a reset, the count direction change flag

(CDCF) is set to “1” on counting up following the reset.

• To enable interrupt requests, the interrupt request permission bit must be set (CFIE=“1”).

• bit13: Enable count direction change interrupt request

When the interrupt request permission bit is set to “1”, the interrupt request flag (CDCF) is enabled.

• bit12: Select internal prescaler

15

14

13

12

11

10

9

8

bit

M16E/

Reserved

CDCF

CFIE

CLKS

CMS1

CMS0

CES1

CES0

UDCCH

0

0

0

0

0

0

0

0

Initial value

R/W *

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Attribute

7

6

5

4

3

2

1

0

bit

Reserved

CTUT

UCRE

RLDE

UDCLR

CGSC

CGE1

CGE0

UDCCL

0

0

0

0

1

0

0

0

Initial value

R/W0

R/W

R/W

R/W

R1,W

R/W

R/W

R/W

Attribute

M16E

Enable 16 bit mode

0

8 bit

× 2 channel operation mode (8 bit mode)

1

16 bit

× 1 channel operation mode (16 bit mode)

CDCF

Direction change detection

When read:

When written:

0

A direction change has not made.

Clear the flag.

1

Direction change has been made once or more.

Writing does not affect the operation.

CFIE

Direction change interrupt request

0

Disable direction change interrupt requests.

1

Enable direction change interrupt requests.

CLKS

Internal clock frequency

0

F

CLKP

/2

1

F

CLKP

/8