FUJITSU MB91460 SERIES FR60 User Manual

Page 818

802

Chapter 39 Programmable Pulse Generator

4.Registers

• Bit 13: Mode selection

• When the Mode Selection bit is set to “0”, a PWM operation is enabled to generate pulses in sequence.

• When the Mode Selection bit is set to “1”, pulse output takes place only once.

• Bit 12: Restart enable

When the Enable Restart bit is set to “1”, a trigger (software/internal) is generated to enable a restart.

• Bits 11-10: Counter clock selection

•

Bit 9: PPG output mask selection

• When the PPG Output Mask Selection bit is set to “1”, the PPG output can be clamped at “L” or “H”

regardless of the mode, cycle, and duty settings.

• The output level can be specified using the Output Polarity Specification bit (PCN.OSEL).

• Bit 8: Undefined.The operation is unaffected by writing. The read value is indeterminate.

• Bits 7-6: Trigger input edge selection

Select an edge to trigger the activation of the trigger input selected with the Trigger Specification bits

(GCN10[15:12]), (GCN10[11:8]), (GCN10[7:4]), and (GCN10[3:0]) of PPG3 to PPG0,

(GCN11[15:12]), (GCN11[11:8]), (GCN11[7:4]), and (GCN11[3:0]) of PPG7 to PPG4,

(GCN12[15:12]), (GCN12[11:8]), (GCN12[7:4]), and (GCN12[3:0]) of PPG11 to PPG8,

(GCN13[15:12]), (GCN13[11:8]), (GCN13[7:4]), and (GCN13[3:0]) of PPG15 to PPG12,

using the Trigger Input Edge Selection bit (EGS[1:0]).

• Bit 5: Interrupt request enable

• Bit 4: interrupt request flag

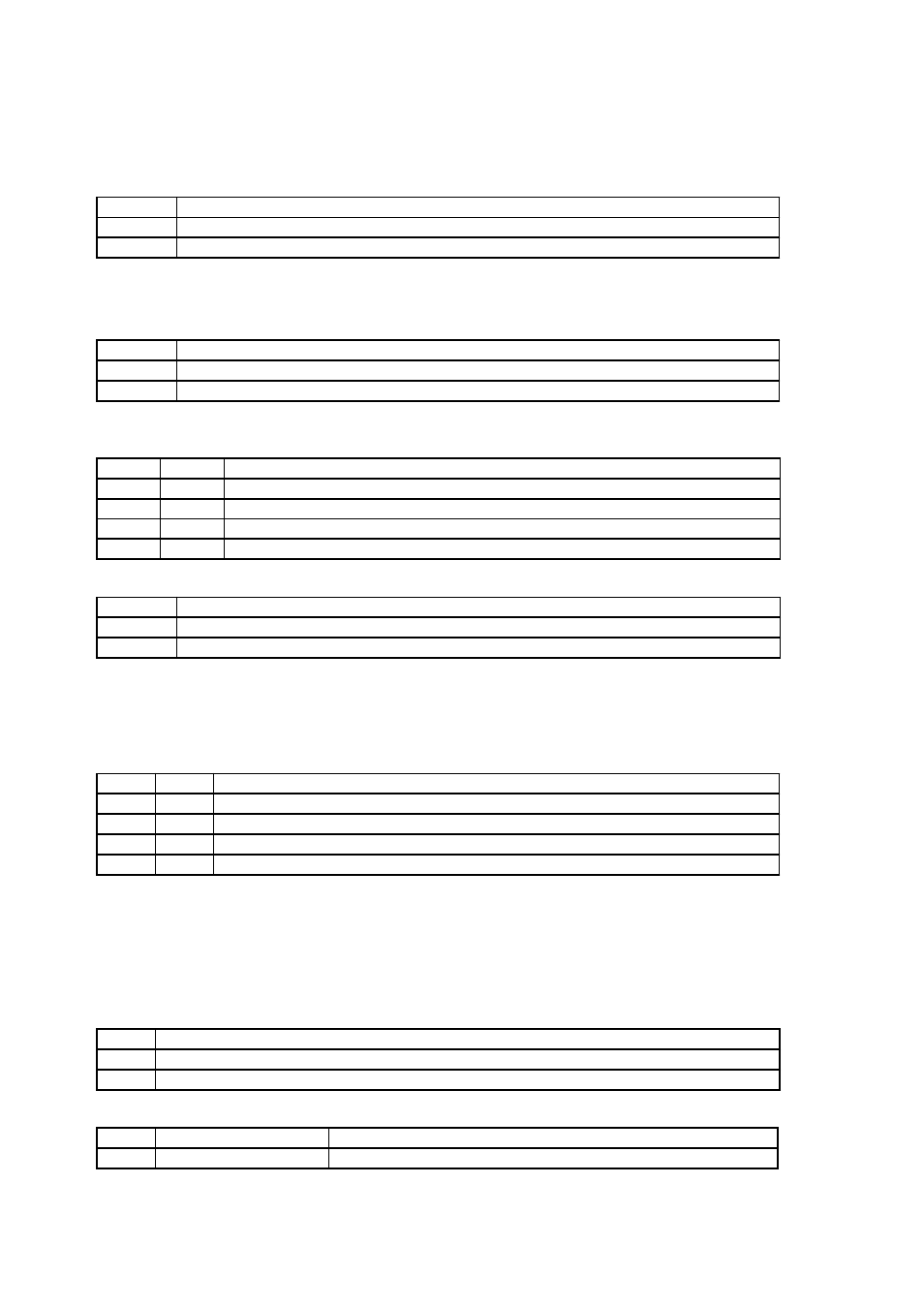

MDSE

Mode

0

PWM operation

1

One-shot operation

RTTG

Operation

0

Disable restart.

1

Enable restart.

CKS1

CKS0

Down Counter Count Clock Selection

0

0

Peripheral clock (CLKP)

0

1

Peripheral clock divided by 4

1

0

Peripheral clock divided by 16

1

1

Peripheral clock divided by 64

PGMS

Operation

0

No output mask

1

Output mask (Output “L” level latched:OSEL=“0”)

EGS1

EGS0

Selected Edge

0

0

The operation is unaffected by writing.

0

1

Rising edge

1

0

Falling edge

1

1

Both edges (rising edge, or, falling edge)

IREN

Operation

0

Interrupt request disable

1

Enable interrupt requests.

IRQF

Read Operation

Write Operation

0

No interrupt request

Clear the Interrupt Request flag.