Configuration, Clock timer – FUJITSU MB91460 SERIES FR60 User Manual

Page 316

300

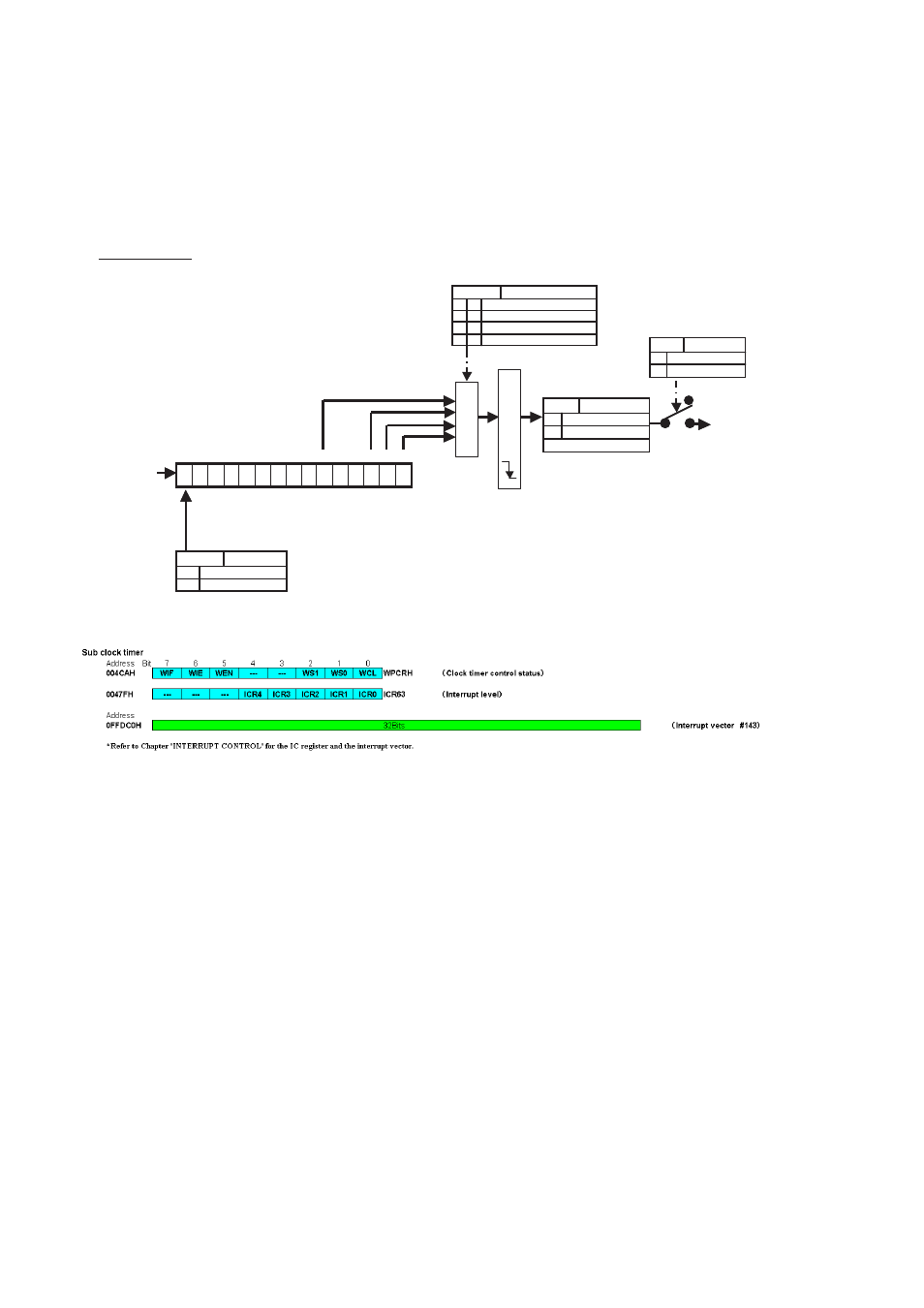

Chapter 23 Sub Oscillation Stabilisation Timer

3.Configuration

3. Configuration

Figure 3-1 Configuration Diagram

Figure 3-2 List of Registers

Note: For the ICR register and interrupt vector, refer to “

Chapter 24 Interrupt Control (Page No.311)

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14

Clock timer

Clock timer

(14-bit free run timer)

Sub-clock

(Source oscillation)

32.768 kHz

WCL

WPCR:bit 2

0

1

Timer clear

Does not affect the operation

Timer clear

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

2

10

2

11

2

12

2

13

2

14

2

15

Selector

Edge detection

WS1-0

WPCR:bit 2-1

0

0

0

Interval time

CL-SUB

CL-SUB

CL-SUB

CL-SUB

2

10

/ F

2

13

/ F

2

14

/ F

2

15

/ F

WIE

WPCR:bit 6

0

1

Interrupt disable

Interrupt enable

Clock timer

Interrupt (#49)

1

0

WIF

WPCR:bit 7

0

1

Without interrupt request

With interrupt request

WRITE; 0: Flag clear

1

1

0

1

1

See also other documents in the category FUJITSU Hardware:

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (76 pages)

- T5140 (102 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)