Chapter 14 pll interface, Overview, Features – FUJITSU MB91460 SERIES FR60 User Manual

Page 223: Frequency calculation, Clkb frequency is determined by, Clkp frequency is determined by, Clkt frequency is determined by

207

Chapter 14 PLL Interface

1.Overview

Chapter 14 PLL Interface

1. Overview

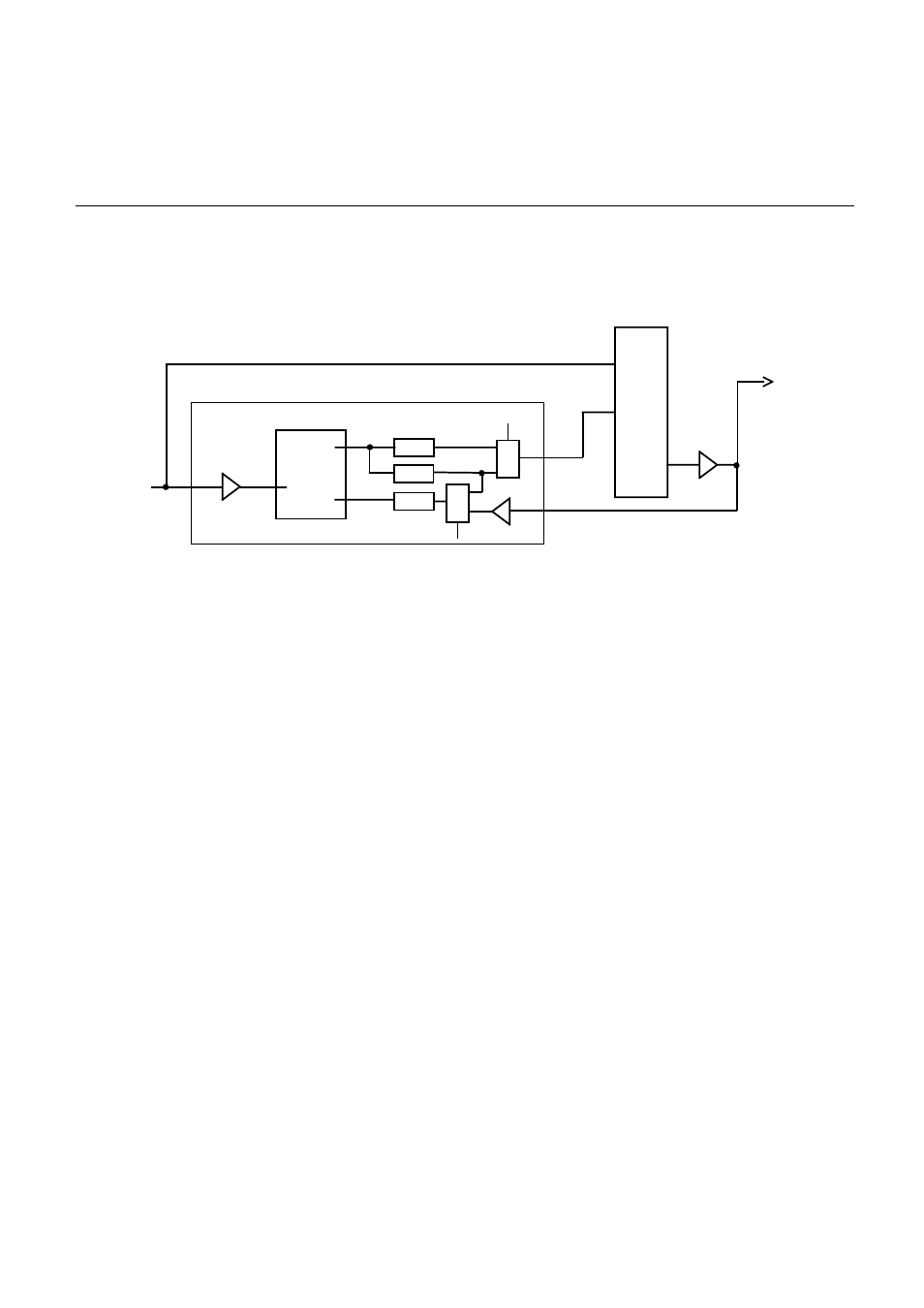

• This blockdiagram (simplified) shows the integration of the PLL and the PLL Interface with the multiplier

control logic (1/M, 1/N for basic frequency multiplication and 1/G for clock auto gear).

2. Features

• Free programmable divide-by-M counter in the range of 1..16

• Free programmable divide-by-N counter in the range of 1..64

• Clock auto gear up/down function to prevent voltage drops and surges

3. Frequency calculation

• CLKB frequency is determined by :

f(CLKB) = [ Main-Osc * (PLLDIVM_DVM+1) *( PLLDIVN_DVN+1) ] / [ (PLLDIVM_DVM+1) * (DIVR0_B+1) ]

• CLKP frequency is determined by :

f(CLKP) = [ Main-Osc * (PLLDIVM_DVM+1) *( PLLDIVN_DVN+1) ] / [ (PLLDIVM_DVM+1) * (DIVR0_P+1) ]

• CLKT frequency is determined by :

f(CLKT) = [ Main-Osc * (PLLDIVM_DVM+1) *( PLLDIVN_DVN+1) ] / [ (PLLDIVM_DVM+1) * (DIVR1_T+1) ]

X

FB

1/M

1/N

Clock Unit

XIN1

PLLIN

FB1 delay

Clocktree

Phase

Correction

1/G

CK

CLKB

CLKP

CLKT

MAIN

Osc.

PLL

Interface

M

U

X

M

U

X

PLL

CPU-Core

Resources

Ext Bus