FUJITSU MB91460 SERIES FR60 User Manual

Page 709

693

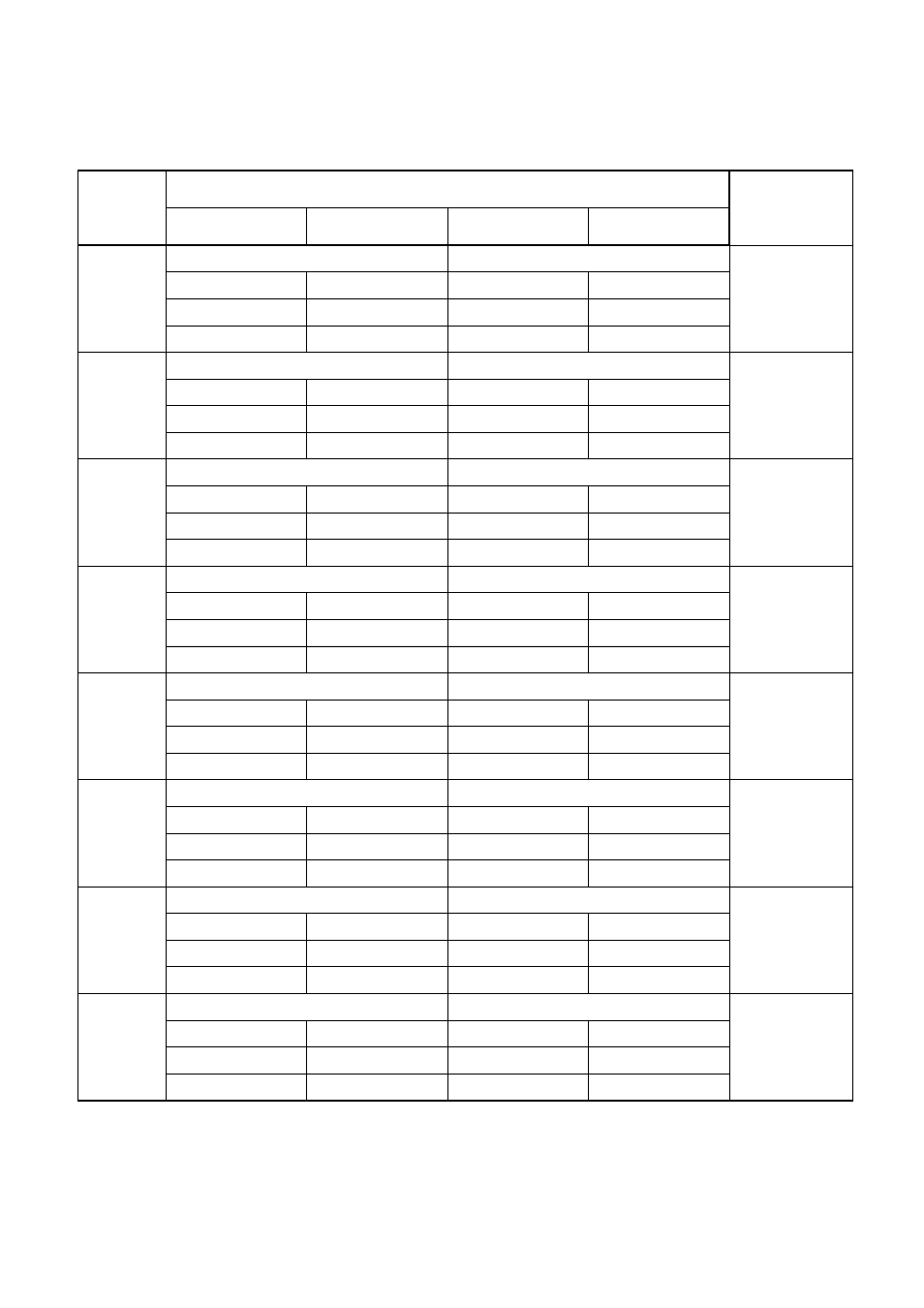

Chapter 34 CAN Controller

2.Register Description

Base-addr +

0x10

IF1 Command Request

IF1 Command Mask

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

Busy

Mess. No. [5:0]

reserved

see descr. IF1CMSK

Reset: 0x00

Reset: 0x01

Reset: 0x00

Reset: 0x00

Base-addr +

0x14

IF1 Mask 2

IF1 Mask 1

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

MXtd,MDir,Msk[28:24]

Msk[23:16]

Msk[15:8]

Msk[7:0]

Reset: 0xFF

Reset: 0xFF

Reset: 0xFF

Reset: 0xFF

Base-addr +

0x18

IF1 Arbitration 2

IF1 Arbitration 1

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

MsgVal,Xtd,Dir,ID[28:24]

ID[23:16]

ID[15:8]

ID[7:0]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x1C

IF1 Message Control

Reserved

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

see descr. IF1MCTR

see descr. IF1MCTR

reserved

reserved

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x20

IF1 Data A1

IF1 Data A2

Big Endian byte

ordering.

bit[7:0]

bit[15:8]

bit[7:0]

bit[15:8]

Data[0]

Data[1]

Data[2]

Data[3]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x24

IF1 Data B1

IF1 Data B2

Big Endian byte

ordering.

bit[7:0]

bit[15:8]

bit[7:0]

bit[15:8]

Data[4]

Data[5]

Data[6]

Data[7]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x30

IF1 Data A2

IF1 Data A1

Little Endian byte

ordering.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

Data[3]

Data[2]

Data[1]

Data[0]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x34

IF1 Data B2

IF1 Data B1

Little Endian byte

ordering.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

Data[7]

Data[6]

Data[5]

Data[4]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Address

Register

Note

+0

+1

+2

+3