Register – FUJITSU MB91460 SERIES FR60 User Manual

Page 317

301

Chapter 23 Sub Oscillation Stabilisation Timer

4.Register

4. Register

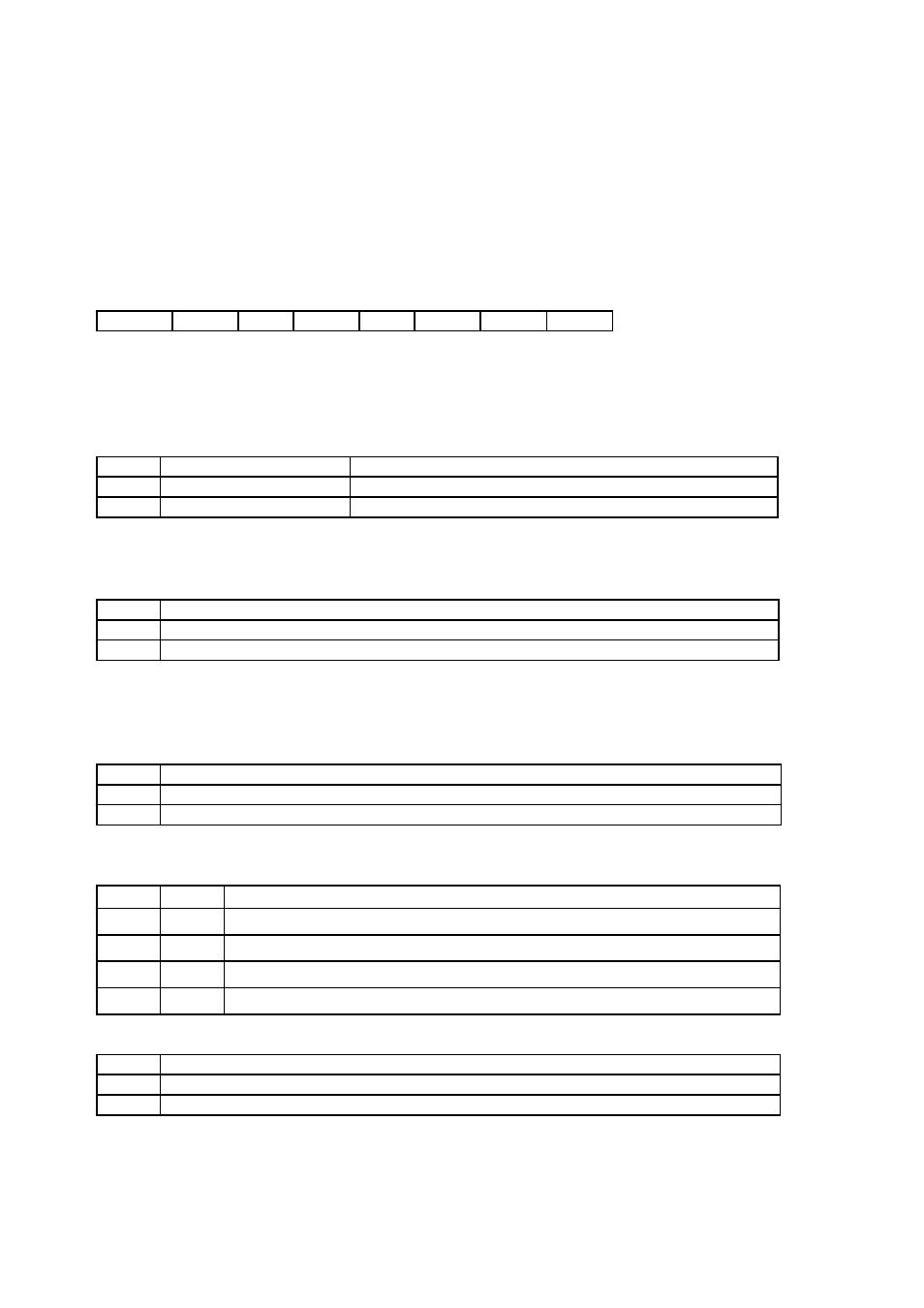

4.1 WPCRH: Sub oscillation stabilisation timer Control Register

This register is used to select interval time, clear the timer, control interrupt, control timer stop etc., and

confirm the states.

• WPCRH: Address 04CAh (Access: Byte)

(For the attributes, refer to “

Meaning of Bit Attribute Symbols (Page No.10)

”.)

(Refer to “

• Bit7: Sub oscillation stabilisation timer interrupt request flag

• The sub oscillation stabilisation timer interrupt request flag bit is set to “1” at the falling edge of the

selected interval period output.

• Bit6: Interrupt request enable

• If the interrupt request enable bit is set to “1” an interrupt request is enabled.

• If the sub oscillation stabilisation timer interrupt request flag is (WIF=“1”), and if the interrupt request

enable bit (WIE) is set to “1”, an interrupt request is immediately generated.

• Bit5: Timer operation enable

• Bit4-3: Reserved bit Be sure to write “0”. The read value is “0”.

• Bit2-1: Interval period selection

• Bit0: Timer clear

• The timer is also cleared by INITX terminal input and watchdog reset.

Notes 1: Initial value can be set using the setting initialization reset (INIT terminal input,

7

6

5

4

3

2

1

0

bit

WIF

WIE

WEN

–

–

WS1

WS0

WCL

0

0

0

X

X

0

0

1

Initial value (At INIT) *1

R(RM1),W

R/W

R/W

RX/W0

RX/W0

R/W

R/W

R1,W

Attribute

WIF

Read Operation

Write Operation

0

Without interrupt request

Clears the interrupt request flag

1

With interrupt request

Writing does not affect operation

WIE

Operation

0

Interrupt request is prohibited

1

Interrupt request enable

WEN

Operation

0

Stops timer operation

1

Enables timer operation

WS1

WS0

Interval period (F

CL-SUB

= 32.768kHz)

0

0

2

10

/F

CL-SUB

(31.25ms)

0

1

2

13

/F

CL-SUB

(0.25s)

1

0

2

14

/F

CL-SUB

(0.50s)

1

1

2

15

/F

CL-SUB

(1.00s)

WCL

Operation

0

Clears the sub oscillation stabilisation timer.

1

Writing does not affect write operation.