FUJITSU MB91460 SERIES FR60 User Manual

Page 249

233

Chapter 16 Clock Supervisor

4.Operation Modes

■

Sub-clock modes

The main clock supervisor is automatically disabled in sub-clock modes. The enable bit MSVE remains

unchanged. At transition from sub-clock mode to main clock mode the main clock supervisor is enabled after the

’oscillation stabilisation wait time’ with the rising edge of signal OSC_STAB or in case the main clock is missing

before the completion of the ’oscillation stabilisation wait time’, after the ’main clock timeout’ (TO_MCLK) from

the timeout counter. The timeout counter is clocked with RC-oscillation clock.

■

Changing the behaviour upon transition to sub-clock mode if the sub-clock has already

stopped in main clock mode

If the sub-clock has stopped in main clock mode and this was detected

by the sub-clock supervisor, the

behaviour upon transition to sub-clock mode depends on the state of the SRST bit.

•

If SRST is set to ’0’ (initial value), reset is not asserted at the transition to sub-clock mode. The transition is

performed using the RC-oscillation clock as sub-clock. In this case it is recommended to check the SM bit

before the transition to sub-clock mode to get the information if sub-clock or RC-oscillation clock is used.

•

If SRST is set to ’1’, reset is asserted at the transition to sub-clock mode.

The following timing diagrams (

,

,

) illustrate this behaviour.

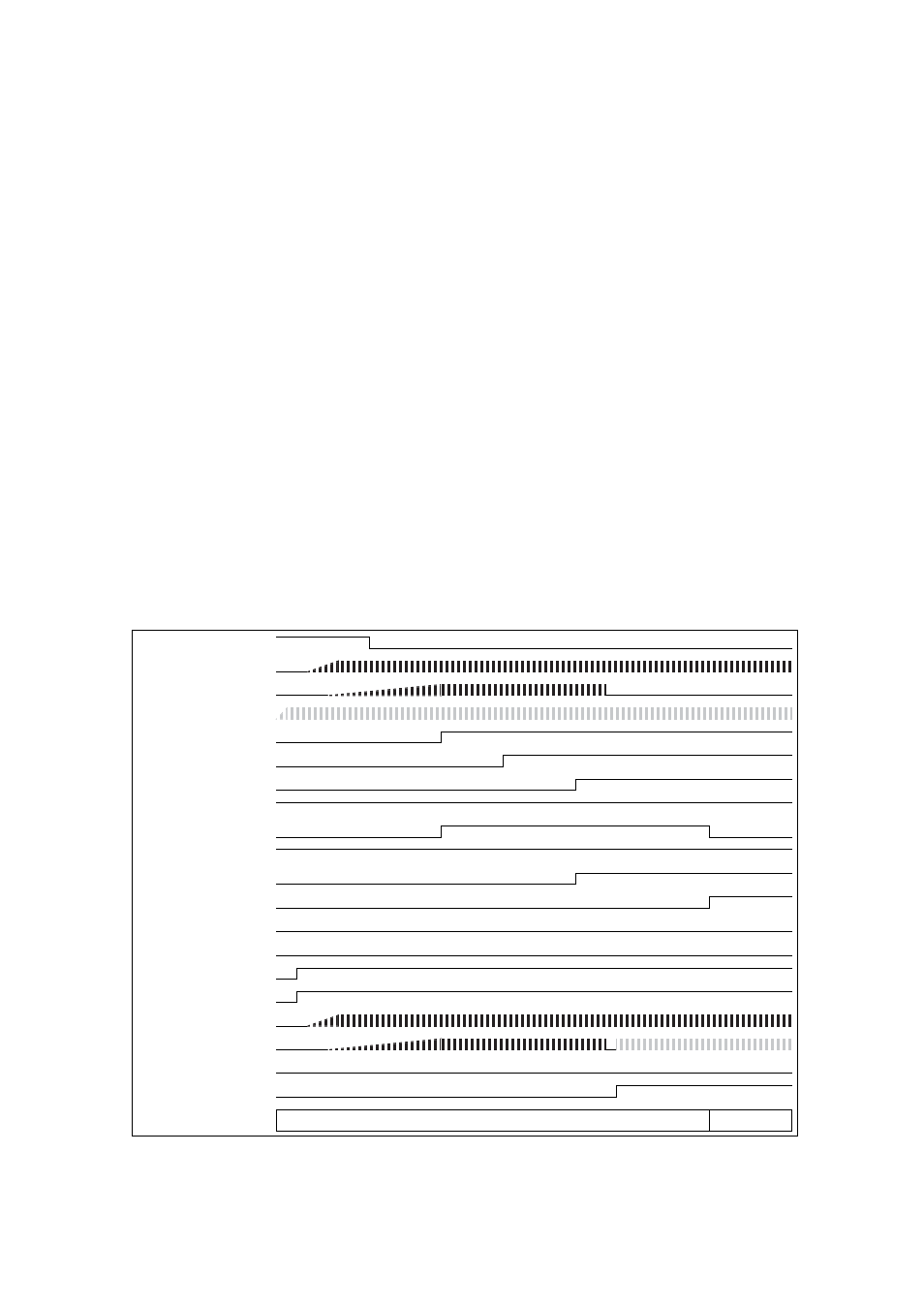

Figure 4-8 Timing Diagram: Sub-clock missing in main clock mode, SRST=0

PONR

MCLK

SCLK

RC_CLK

OSC_STAB

MSVE

MSEN

SSVE

SSEN

MCLK_STBY

SCLK_STBY

TO_MCLK

TO_SCLK

EXT_RST

EXT_RST_OUT

MCLK_OUT

SCLK_OUT

MCLK_MISSING

SCLK_MISSING

SRST

Clock Mode

Main

Sub