FUJITSU MB91460 SERIES FR60 User Manual

Page 444

428

Chapter 29 MPU / EDSU

4.Registers

This register sets the 32 bit comparison value for break point 1 of CMP0. In range mode (set with ER0) the register

value of BAD1 functions as upper address limit.

In the special case of MPE=1 and COMB=1 BAD1 is not used for the point definition. CMP0 gets its point configu-

ration then from BAD3.

This register sets the 32 bit comparison value for break point 2 of CMP1. In range mode (set with ER1) the register

value of BAD2 functions as lower address limit. In addition BAD2 could be used as mask register.

This register sets the 32 bit comparison value for break point 3 of CMP1. In range mode (set with ER1) the register

value of BAD3 functions as upper address limit.

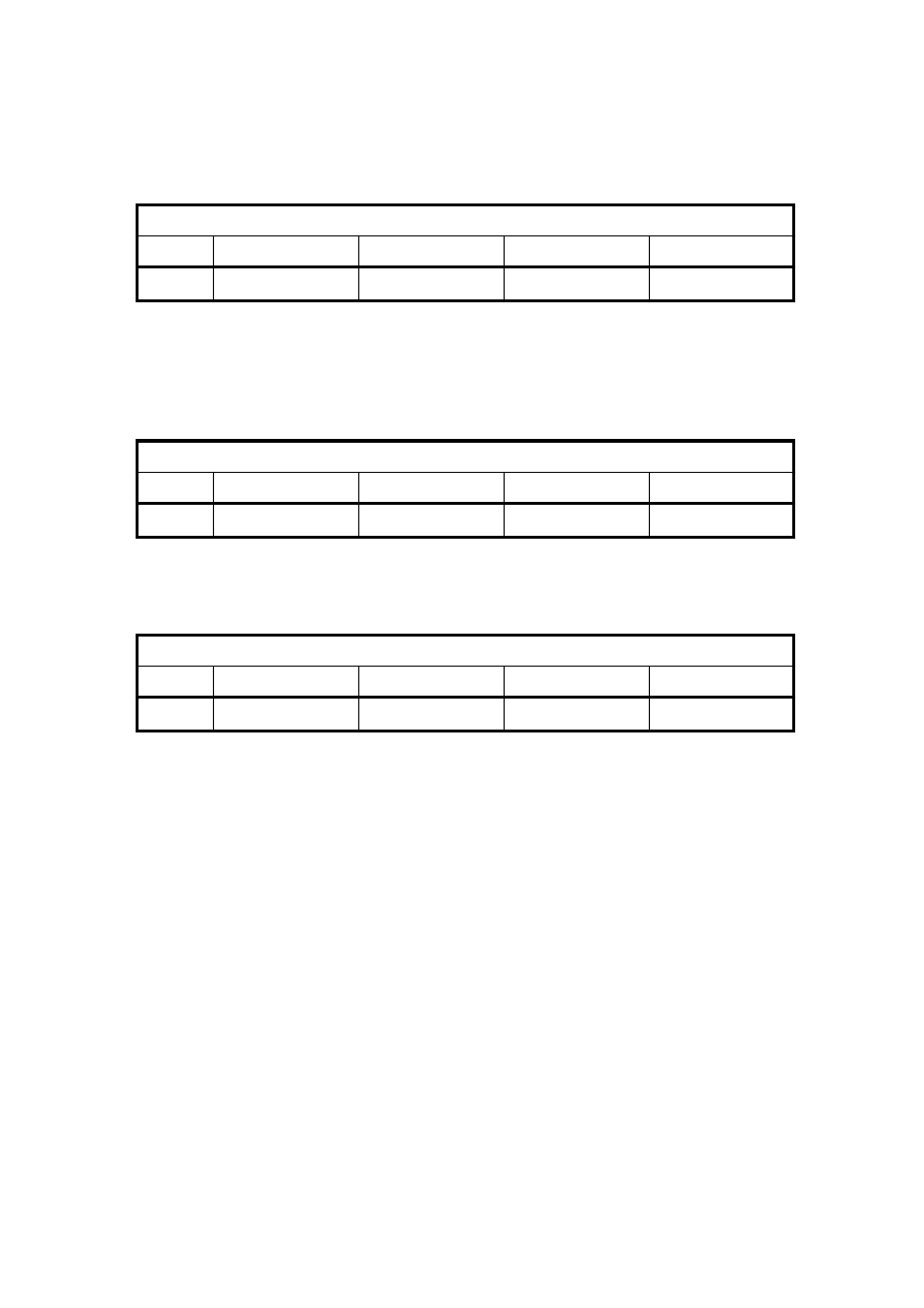

BAD1 (BAD5 BAD9, ..., BAD29) [R/W]

Address

+0

+1

+2

+3

F084

H

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

BAD2 (BAD6, BAD10, ..., BAD30) [R/W]

Address

+0

+1

+2

+3

F088

H

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

BAD3 (BAD7, BAD11, ..., BAD31) [R/W]

Address

+0

+1

+2

+3

F08C

H

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)